## **Description of Goods and Services**

## SuperMUC-NG

(August 21, 2017)

### Aug 2017

#### Direktorium: Prof. Dr. D. Kranzlmüller (Vorsitzender), Prof. Dr. Dr. A. Bode Prof. Dr. H.-J. Bungartz, Prof. Dr. H.-G. Hegering

Leibniz-Rechenzentrum Boltzmannstraße 1 85748 Garching b. München Telefon: +49 89 35831 - 8000 Telefax: +49 89 35831 - 9700 USt-IdNr.: DE811335517

lrzpost@lrz.de . www.lrz.de

E-Mail: Internet:

LRZ-Bericht 2017-2

| 1G   | Seneral information on the RFP                                                                                                | 1  |

|------|-------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1  | Introduction                                                                                                                  | 1  |

| 1.2  | General objectives for the SuperMUC-NG Tier-0/Tier-1 system                                                                   | 2  |

| 1.3  | LRZ System Concept                                                                                                            |    |

| 1.4  | Potential sources for performance increase                                                                                    |    |

| 1.5  | Two-phase installation                                                                                                        |    |

| 1.6  | Draft schedule for installation                                                                                               |    |

| 1.7  | Categorization of requirements                                                                                                |    |

| 1.7  | Requirements with respect to the content of the proposal                                                                      |    |

| 1.9  | Sources for requirements                                                                                                      |    |

|      | Checking of requirements                                                                                                      |    |

|      |                                                                                                                               |    |

|      | Additional material                                                                                                           |    |

| 1.12 | 2 Glossary                                                                                                                    |    |

| 2P   | Project Management Requirements                                                                                               |    |

|      |                                                                                                                               |    |

| 2.1  | Project Management                                                                                                            |    |

| 2.2  | Risk Assessment                                                                                                               | 14 |

| 3 R  | Requirements for SuperMUC-NG                                                                                                  | 17 |

|      |                                                                                                                               |    |

|      | Installation requirements                                                                                                     |    |

|      | 3.1.1 Proposal for installation                                                                                               |    |

|      | 3.1.3 Installation Locations                                                                                                  |    |

|      | 3.1.4 Conformity with electrical standards                                                                                    |    |

|      | 3.1.5 Power supply                                                                                                            |    |

|      | 3.1.6 Cooling<br>3.1.7 Documentation and Labelling                                                                            |    |

| 3.2  |                                                                                                                               |    |

|      | 3.2.1 Overall System Architecture                                                                                             |    |

|      | 3.2.2 General Purpose Compute Nodes                                                                                           |    |

|      | 3.2.3 Configuration of the Compute Nodes                                                                                      |    |

|      | 3.2.4 Optional: Many-Core Nodes                                                                                               |    |

|      | 3.2.5 Optional: Accelerated Nodes                                                                                             |    |

|      | <ul><li>3.2.6 Variability of the Compute Nodes</li><li>3.2.7 Login and Service Nodes</li></ul>                                |    |

| 3.3  | High-Performance Interconnect                                                                                                 |    |

|      | 3.3.1 General objectives                                                                                                      |    |

|      | 3.3.2 Interconnect within and between Islands                                                                                 |    |

|      | 3.3.3 Interconnect between Phase 1 and Phase 2                                                                                |    |

|      | 3.3.4 Dynamic routing and congestion control                                                                                  |    |

|      | <ul><li>3.3.5 Quality of Service of the High-Performance Interconnect</li><li>3.3.6 Connection to external networks</li></ul> |    |

| 3.4  | Configuration of Phase 2 and the combined Phases 1+2                                                                          |    |

|      | 3.4.1 Extent of inhomogeneity of Phase 1 and Phase 2                                                                          |    |

|      | 3.4.2 Performance of Phase 2                                                                                                  |    |

| 3.5  | Storage                                                                                                                       |    |

|      | 3.5.1 Overview                                                                                                                |    |

|      | 3.5.2 Common Requirements                                                                                                     |    |

|      | 3.5.3 Data Science Storage (DSS) style systems                                                                                |    |

|      | 3.5.4 DSS HOME requirements                                                                                                   |    |

|      | 3.5.7 High Performance Parallel File Systems                                                                                  |    |

|      | J J                                                                                                                           |    |

| 3.5.8 Location of Storage Systems                                                         | 59 |

|-------------------------------------------------------------------------------------------|----|

| 3.5.9 Phase 2 Storage                                                                     |    |

| 3.6 Technical Infrastructure for Energy Efficient Operation                               |    |

| 3.6.1 Energy and Power Measurements                                                       |    |

| 3.6.2 Reuse of Waste Heat                                                                 |    |

| 3.7 Reliability and Fault Tolerance                                                       |    |

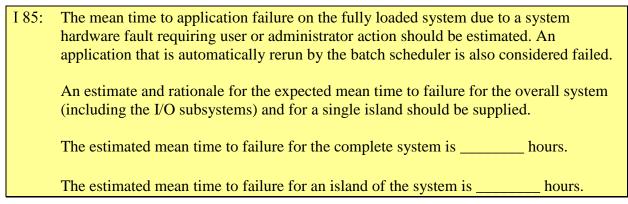

| 3.7.1 Mean time to Failure and Lifetime                                                   |    |

| 3.7.2 Power Cycling                                                                       |    |

| 3.7.3 Power Ramps                                                                         |    |

| 3.7.4 Detection of Hardware Faults                                                        |    |

| 3.7.5 Log File Aggregation with SPLUNK                                                    |    |

| 3.7.6 Fault Isolation                                                                     |    |

| 3.7.7 On Site Stock Keeping of Replacement Parts                                          |    |

| 3.8 Operating System                                                                      |    |

| 3.8.1 Standards                                                                           | 66 |

| 3.8.2 Diskless Nodes                                                                      |    |

| 3.8.3 Checkpoint/Restart                                                                  |    |

| 3.8.4 Suspend/Resume                                                                      |    |

| 3.8.5 Detection and Handling of Resource Overuse                                          |    |

| 3.9 Resource Management and Batch Scheduling                                              |    |

| 3.9.1 General Objectives                                                                  |    |

| 3.9.2 Specific Job Handling                                                               |    |

| 3.9.3 Energy and Topology Awareness                                                       |    |

| 3.9.4 Allocation of nodes and access to the nodes                                         |    |

| 3.9.5 Reporting                                                                           |    |

| 3.9.6 Additional Requirements                                                             |    |

| 3.10 System Management                                                                    |    |

| 3.10.1 System Administration                                                              |    |

| 3.10.2 Test System                                                                        |    |

| 3.10.3 Monitoring                                                                         |    |

| <ul><li>3.10.4 IT Security</li><li>3.10.5 System Restarts and Upgrades</li></ul>          |    |

| 3.11 Support, Documentation and Training                                                  |    |

|                                                                                           |    |

| <ul><li>3.11.1 Problem Solving Mechanisms</li><li>3.11.2 System-Related Support</li></ul> |    |

| 3.11.2 System-Related Support                                                             |    |

| 3.11.4 Documentation                                                                      |    |

| 3.11.5 Introduction to the System                                                         |    |

| 3.12 Software                                                                             |    |

| 3.12.1 Programming Models                                                                 |    |

| 3.12.2 Major Software Components                                                          |    |

| 3.12.3 MPI: Message Passing Interface                                                     |    |

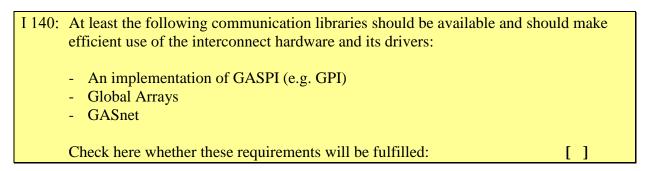

| 3.12.4 Other Communication Libraries                                                      |    |

| 3.12.5 Compilers                                                                          |    |

| 3.12.6 Other Compilers, Libraries, Components and Development Tools                       |    |

| 3.12.7 Task and Thread Location and Pinning                                               |    |

| 3.12.8 Stack Traces and Lightweight Core Files                                            |    |

| 3.12.9 Libraries                                                                          |    |

| 3.12.10 Scope of Support for Scientific Libraries                                         |    |

| 3.12.11 Programming Environment and Tools                                                 |    |

| 3.12.12 Availability of Applications and Libraries                                        |    |

| 3.12.13 Virtualization of the Software Environment                                        |    |

| 3.13 Migration Path                                                                       |    |

| 3.14 Cloud Resources and Remote Visualization                                             |    |

| 3.14.1 Cloud Concept                                                                      |    |

| 3.14.2 Cloud Hardware                                                                     |    |

| 3.14.3 SuperMUC-NG Gateway to the Cloud                                                   |    |

| 3.14.4 Interfacing of SuperMUC-NG with the Cloud                                          |    |

| 3.14.5 Grid Software                             |  |

|--------------------------------------------------|--|

| 3.14.6 Remote Visualization                      |  |

| 3.15 Maintenance                                 |  |

| 3.16 Market Penetration                          |  |

| 3.17 Price and Scaling                           |  |

| 3.18 Collaboration with the Tenderer             |  |

| 3.19 Benchmarks                                  |  |

| 4 Tables of Key System Parameters                |  |

| 4.1 System Reliability                           |  |

| 4.2 Test System                                  |  |

| 4.3 Infrastructure                               |  |

| 4.4 Compute Node Architecture                    |  |

| 4.4.1 General Purpose Compute Nodes              |  |

| 4.4.2 Optional: Many-Core Nodes                  |  |

| 4.4.3 Optional: Accelerators (Accelerated Nodes) |  |

| 4.4.4 Optional: Specialized Memory Architectures |  |

| 4.5 High Performance System Interconnect         |  |

| 4.6 IO Subsystem                                 |  |

### **1** General information on the RFP

### **1.1 Introduction**

Apart from theory and experiment, simulations on HPC systems are now established as indispensable instruments for most scientific disciplines as well as for industry. This was one reason for the German Federal Government and for the States of Baden-Wuerttemberg, Bavaria, and North Rhine-Westphalia for creating the Gauss Centre for Supercomputing (GCS) as a leadership HPC infrastructure for science in Germany and Europe in 2007. As part of this effort, three multi-petascale systems were installed in staggered order at the national centres JSC in Juelich, HLRS in Stuttgart and LRZ in Garching. Also, a technical diversity of the GCS systems, programming models and system software was ensured.

A second round of funding for the three centres is announced for the timeframe of 2017-2025, under the project designation SiVeGCS.

The current system operated by LRZ is SuperMUC, a 6.6 PFlop/s system from IBM and Lenovo. It is comprised of standard Xeon architecture nodes and uses a novel form of direct warm water cooling developed by IBM, which made it one of the most energy-efficient systems in the world.

SuperMUC is used for a broad range of applications from many areas of science, in particular astrophysics, plasma and high energy physics, earth and environmental sciences, life and material sciences, engineering as well as computational fluid dynamics. Information about the scientific projects and results from SuperMUC can be found in the book series

High Performance Computing in Science and Engineering-Garching/Munich,

which are also electronically available<sup>1</sup>.

The successor of the current system at LRZ, codenamed SuperMUC-NG ("SuperMUC Next Generation"), is again intended for use as a national Tier-1 high performance computing resource as well as a European Tier-0 system in the context of the PRACE research infrastructure<sup>2</sup>. SuperMUC-NG will be operated by the Leibniz Supercomputing Centre (LRZ) of the Bavarian Academy of Sciences and Humanities on behalf of the Gauss Centre for Supercomputing. SuperMUC-NG is expected to deliver outstanding international application performance for a wide range of user applications and to achieve one of the top positions among supercomputers worldwide.

<sup>&</sup>lt;sup>1</sup> https://www.lrz.de/services/compute/supermuc/magazinesbooks/index.html#Books

<sup>&</sup>lt;sup>2</sup> http://www.prace-ri.eu/

# 1.2 General objectives for the SuperMUC-NG Tier-0/Tier-1 system

The range of applications targeted for deployment on SuperMUC-NG will be comparable to that on the current system, and is expected to widen into additional scientific domains. Also, the future job profile will impose demands on compute performance, memory size and bandwidth, network latency and bandwidth as well as storage capacity and bandwidth of the system it executes on, that cannot be fulfilled by the currently deployed technology. SuperMUC-NG should therefore be a system characterized by leading-edge performance and reliability in all aspects of its delivered hardware.

The amount of data produced by traditional HPC and upcoming Big Data applications requires data centric memory and storage hierarchies. Furthermore, a robust and scalable software stack and programming environment is of major importance. It should enable users to build, debug and reliably run applications that use the entire system.

It is the explicit goal of the LRZ to provide these services without imposing many additional constraints on its current and future user base. To this end, only a computing system that is usable in a highly versatile manner will be considered for acquisition. Special-purpose architectures that offer advantages for only a small subset of algorithms and applications will not be taken into consideration. Following this, the primary goal for the procurement of SuperMUC-NG is:

To establish a reliable and versatile leadership-class system for large-scale compute and data-intensive workloads.

With an expected compute power of SuperMUC-NG Phase 1 an order of magnitude higher than the current system, efficient execution of large jobs is a matter of great importance. However, extensive parameter studies using many small and medium-sized jobs are very common in many scientific areas, e.g. replica exchange methods in molecular dynamics or data processing of Large Hadron Collider experiments. Furthermore, a steadily growing number of projects demand the support of complete application workflows, or virtualization concepts such as Cloud Computing. Efficient support of such user requirements should therefore be possible on the new supercomputer.

The use of cutting-edge numerical algorithms as well as careful program development and debugging are mandatory requirements for the efficient usage of modern supercomputer resources, particularly, regarding the proficiency that modern multi- and many-core processors demand with respect to parallel program design. Within this context, the theoretical peak performance of the system is less important than sustained system performance for the entire spectrum of applications of LRZ's current and future user base. For the assessment of the SuperMUC-NG application performance all Tenderers must commit to performance numbers for a set of real application as well as synthetic benchmarks. Please refer to the document "Decision Criteria and Benchmark Description SuperMUC-NG" for further details on the SuperMUC-NG benchmark suite and evaluation schemes.

Given the usage profile of the current SuperMUC system, the acquisition goal is to install a heterogeneous supercomputer based on general purpose compute nodes, and, to a small extent, of compute nodes with large shared memory. A significant part of the system may be composed of many-core or accelerated compute nodes. All compute nodes must be connected via a common high-speed network.

Because programs will have run times up to several days, the offered SuperMUC-NG system must provide a high degree of stability and usability under permanent load with changing usage profiles. Finally, reliable file systems are required to ensure the integrity and availability of scientific data.

## 1.3 LRZ System Concept

In its concept for SuperMUC-NG, LRZ starts out from the assumption that many current and future projects will tackle problem sizes with parallel code that can no longer be completed in reasonable time on a quarter of the current system. The system design of SuperMUC-NG must ensure that such applications can be executed with leading edge application performance. However, it should not negatively impact medium sized parameter studies and high throughput requirements.

LRZ envisions that the system will be composed of **islands of highly interconnected compute nodes with non-blocking or nearly optimal communication links between all nodes within an island.** It is desired that each island either contains at least **1024 compute nodes** or provides a (double precision floating point) peak performance of at least **1.5 PFlop/s.**

The link bandwidth and the number of links for the **communication between these islands** may have smaller aggregate bandwidth than within an island (**pruned interconnect**<sup>3</sup>) depending on the involved costs and the deployed technology. The rationale and experience underlying the pruned interconnect requirement between islands are:

- Many communication patterns are of nearest-neighbor type and do not need a full set of links across islands due to the volume-surface ratio of data exchange.

- Large-scale applications, which need more cores than one island provides, may be scheduled round-robin over all or many islands and may consume the link bandwidth that is not used by other applications that are running entirely in one island.

The above considerations assume a fat tree network topology. However, **other implementations of network topologies** such as multi-dimensional torus or dragonfly network topologies are also considered acceptable, especially if no substantial commercial or technical advantage can be gained by implementing a pruned fat tree network topology.

It is expected that **topology-aware placement** of jobs will be necessary for most solutions, handling of which should be flexible and easy to manage. It is also desired that **adaptive routing** algorithms prevent contention within the interconnect network, as well as provide failover or fast re-routing in case of hardware failures. Provisions for controlling the **quality of service** for specific services and controlling congestion are also of interest.

For the bulk of the system, two options may be considered, either **stand-alone many-core nodes** or **thin shared memory nodes** that optionally may contain **one or more accelerators** ("GPGPUs").

**Stand-alone many-core nodes** should contain at least 96 GBytes of main memory and might also contain a sizeable portion of **high bandwidth memory**.

<sup>&</sup>lt;sup>3</sup> The term "pruned interconnect" is used for tree topologies in which the connection of the highest switch level hierarchies is realized with a reduced number of network links compared to a fat tree.

Thin shared memory nodes that optionally may contain one or more accelerators ("GPGPUs") should contain at least 40 physical cores of a general-purpose architecture, and sufficient memory to ensure that at least 2 GBytes per core are available to an MPI application in user space if the node is completely filled with MPI tasks. For accelerated nodes, it must be assured that ease of programming and efficient use are not significantly curtailed compared to a general-purpose architecture. In particular, it may be necessary to equip accelerated nodes with significantly more main memory to achieve proper balancing of compute power against memory requirements of applications.

Whatever node design is chosen for the bulk of the system, the **general purpose compute performance** (i.e. excluding accelerators or many-core nodes) of SuperMUC-NG Phase 1 **should not be less than** the compute performance of SuperMUC Phase 2.

The aggregate size of the DDR-based main memory of the Phase 1 system should exceed 500 TBytes.

To provide similar shared memory characteristics as those presently available on the "fat" node island of SuperMUC Phase 1, the new system should supply a number of large shared memory nodes.

**Message passing** will continue to be the dominant programming paradigm and will be used for coarse-grained parallelism. Consequently, the system must be equipped with an **efficient internal interconnect** as well as an **efficient MPI implementation** that makes optimal use of the hardware and optionally off-loads workload to the network devices. Efficient implementations for the evolving **PGAS** (**Partitioned Global Address Space**) programming languages are desired.

The experience of LRZ shows that efficient parallelization is easier to achieve with a moderate number of high-performance shared-memory computational units than with many low-performance units. Therefore, most if not all users will utilize **the hybrid programming model** with MPI between such units, and auto-parallelization, OpenMP or OpenACC within the units. Both experiences and theoretical considerations show that for achieving optimal performance with the hybrid model, a **fully thread-safe** implementation of all relevant libraries (specifically MPI) is essential.

A complete HPC software stack necessary for development and deployment of scientific and technical applications must be available (a Linux-based operating system suitable for deployment on the targeted system, highly efficient system drivers for interconnect and I/O, highly efficient compilers, optimized libraries, tools, ISV applications). Support for efficient execution of the most commonly used scripting languages and problem solving environments is considered important. Domain specific languages, machine learning and scalable data analytics will become increasingly important on HPC systems.

Rapid deployment of applications can be aided by **virtualization** concepts; it should therefore be possible to pack an application and its dependencies into a virtual **container**. This concept of HPC node virtualization will give users the opportunity to tailor and adapt the run-time environment to the needs of their applications.

Together with the compute nodes, the Tenderer must offer sufficiently **large**, efficient, secure and reliable storage systems for user data. The integrity of the data must be assured, since in the many-petabyte regime dump-restore of file systems is no longer feasible. Advances in software technologies will be necessary for both the management and efficient usage of the storage subsystems.

The usage profile calls for two types of storage:

- A **parallel file system**, which should contain temporary data and the large result files (termed SCRATCH and WORK). For these data, **high I/O bandwidth** and moderate metadata performance are needed. Specialized support for efficient parallel I/O to a single file from multiple nodes is expected. This storage component must be integrated with the system via the high-performance network.

- Highly reliable **home and project file systems** for user data (HOME and PROJECT), such as source and input files, libraries, configuration and simulation data sets. Metadata performance should be very high, while bandwidth may be moderate. The requirements for reliability, availability and for data safety are very high. In addition, **the accessibility of user data should not depend on the operating condition of SuperMUC-NG**. LRZ has excellent experiences with IBM Spectrum Scale storage (formerly GPFS) and is operating and extending a GPFS-based **Data Science Storage (DSS)** for this purpose.

The leverage of **cloud mechanisms** via a **login cloud** should provide universal and simplified access to the HPC resources and the data residing on the system. Main goals for the login cloud are:

- To provide the users a programming environment

- To give users access control for their data, also for access from the outside world

- To give users the possibility to construct portals for access

- To provide means for pre- and post-processing, and for remote visualization

Only the hardware needed for the cloud (including hardware maintenance) need to be offered within this procurement, and some level of support in interfacing the cloud component with the computational system.

Outside the scope of this procurement, **systems for archiving and backup** will be acquired. It is required that these systems are efficiently connected and operated together with SuperMUC-NG. Therefore, the necessary hardware and software interfaces for this connection are part of this procurement.

Finally, a **software porting and transition path** from the current system to the new one should be established. The tradeoff between potential performance gains and the necessity as well as the extent of algorithmic changes should be assessable.

### **1.4** Potential sources for performance increase

LRZ considers the following technologies as potential sources for further increasing the performance of HPC systems:

- Growth of the number of cores and threads within general purpose nodes

- Accelerated nodes (GPUs or many-core)

- Further increase of peak performance by means of vectorization

- High Bandwidth Memory, whether directly addressed or used as large cache, in addition to or in lieu of DRAM

- Use of non-volatile memory/storage class memory for efficient I/O

- Faster and better-integrated interconnects

- New interconnect topologies, dynamic routing and resource scheduling

- Fast connection links between node-attached accelerators and host processors (e.g. NVLINK)

- Improved energy efficiency

- Improved scalability

On the software side LRZ sees the following important technologies:

- Extensions of directive-based (OpenMP, OpenACC) programming models for accelerated node architectures

- Extension of existing development, debugging and tuning tools to encompass accelerated node architectures while maintaining ease of use

- Support for the efficient management of data staging between various levels of storage, and for the management of checkpoint data that need to be available for a new job instance

- Availability of resilience features in the batch scheduling component as well as in the parallel programming APIs/semantics to enable continuing job execution even if the nodes assigned to that job fail

- Availability of domain specific libraries and frameworks

- Programming methods that permit to reduce the message passing overheads (MPI+X)

- Implementation of e.g. PGAS programming languages as a complement to message passing for higher programming productivity on distributed memory architectures.

The response to this RFP should take these technologies into consideration. The above items are not intended to limit the system selection; other innovative approaches that might realistically be deployed in the procurement time frame can become part of an offer. Also, the order in which the above items appear do not imply a priority.

## **1.5** Two-phase installation

The installation of SuperMUC-NG shall proceed in two phases:

- Installation of **Phase 1** of the system should start early in **2018** and be completed by the **end of 2018**.

- **Phase 2**<sup>4</sup> should be installed approximately two and a half years after operational readiness of Phase 1. It should deliver a substantial performance increase compared to Phase 1.

Phase 2 may consist of installing **additional nodes or of a replacement** of the Phase 1 system. The upgrade should neither involve an interruption of Phase 1 operation that takes longer than a typical maintenance interval, nor a serious degradation of performance and stability of Phase 1 operation.

For submission of the bid, the Tenderer needs to supply a conceptual description for Phase 2. A commitment of the performance increase must be delivered. The technical possibilities, the required additional porting effort, and the capability of interoperating Phase 1 with the upgrade must be described.

## **1.6 Draft schedule for installation**

A **draft schedule** for the Site Preparation and Installation Plan (see Section 3.1.2) for SuperMUC-NG is given in the following table.

| Milestone or activity                                                | Estimated dates and major dependencies                                  | Referenced in Section |

|----------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------|

| Site preparation and installation plan                               | "At most three months after signing of the contract"<br>Q1/2018         | 3.1.1                 |

| Data Science Storage<br>delivered, installed and<br>accepted         | delivered, installed and                                                |                       |

| Phase 1 Test system<br>(incl. management)<br>delivered and installed | Several months in advance before "Phase 1<br>delivery of main hardware" | 3.10.2                |

| Phase 1 system<br>management components<br>delivered and installed   | Three months before "Phase 1 delivery of main hardware"                 | 3.10.1                |

| Site preparation by vendor                                           | Expected in Q1 2018                                                     |                       |

| Phase 1 delivery of main hardware                                    | Preferably started in Q2/2018                                           |                       |

| Phase 1 of previous LRZ<br>supercomputer is<br>decommissioned        | End of January, 2019                                                    |                       |

| Completion of Phase 1                                                | Preferably in Q3/2018                                                   |                       |

| system installation                                                  | Expected in early Q4/2018                                               |                       |

| System Readiness<br>("Betriebsbereitschaft")                         | Expected November 1, 2018                                               |                       |

| Earliest possible<br>acceptance of Phase 1                           | System Readiness + 30 calendar days                                     |                       |

| Latest possible<br>acceptance of Phase 1                             | System Readiness + 100 calendar days                                    |                       |

| Installation of Phase 2                                              | Approximately two and a half years after<br>system readiness of Phase 1 |                       |

## **1.7** Categorization of requirements

All requirements of this procurement that will be relevant for acceptance testing fall into one of three categories; these are indicated by the appearance of colored boxes:

| М | <ul> <li>Requirements within red boxes and marked by "M" are considered mandatory. Offers that do not indicate fulfillment of any mandatory requirement will be excluded from the procurement process.<sup>5</sup></li> <li>Such requirements include the phrase MUST or MUST NOT.</li> </ul>                                                                                                                                                                                                |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ι | <ul> <li>Requirements within yellow boxes and marked by "I" are considered <b>important</b> for the operation and usability of the system.</li> <li>Offers that fail to fulfill such a requirement will remain included in the procurement process if they specify alternatives that adequately cover the needed functionality. The proposed alternatives and their implications must be explained in detail.</li> <li>Such requirements include the phrase SHOULD or SHOULD NOT.</li> </ul> |

| Т | <ul> <li>Requirements within green boxes and marked by "T" are considered targets for the proposed system.</li> <li>An offer that fulfils these requirements can achieve a qualitatively better ranking through the evaluation procedure.</li> <li>Such requirements include the words MAY, OPTIONAL, IS PREFERRED or IS DESIRED.</li> </ul>                                                                                                                                                 |

Many requirements contain checkboxes. All checkboxes must be filled in as follows:

[X] a checkbox marked by the Tenderer with "X" indicates that the requirement will be fulfilled and the feature is included in the Tenderer's offer.

**[O]** a checkbox marked by the Tenderer with "O" indicates that the requirement **cannot be fulfilled**.

## **1.8** Requirements with respect to the content of the proposal

For all requirements contained in this document, an offer must indicate whether they can be fulfilled or not. If the former is the case, the offer must provide an explanation how the Tenderer intends to fulfil the given requirements.

If not explicitly stated otherwise, the offer must provide detailed information only for Phase 1.

The answers should refer only to offered goods and services. Answers and explanations must be inserted into the appropriate sections of this document and should be as concise as possible. However, any relevant difference between Phase 1 and Phase 2 must be explained in this description. Wherever appropriate and possible, there should be references to common standards of information technology. Bibliographical references (e.g. brochures and manuals)

<sup>&</sup>lt;sup>5</sup> cf. "Anschreiben SuperMUC-NG"

are desirable but can only be considered as supplementary information i.e. they cannot replace the required answers or explanations.

Unanswered or insufficiently answered questions will be considered as answered in the negative.

The Tenderer is encouraged to provide additional information at or near the end of a subsection. However, the Tenderer should not rephrase/reiterate the requirements.

The Tenderer may hand in the specifications stipulated below in German or English or a mixture of both. The Tenderer should use the provided fields at or near the end of most subsections that are labelled as follows:

" [Insert text here] "

The supplied text should be clearly structured such that the reader can deduce which requirement is being referred to.

### **1.9** Sources for requirements

The primary sources of requirements can be grouped into the following categories. LRZ will evaluate how well the proposed solution satisfies the resulting requirements.

| Category | The requirement is specified because                                                                                               |

|----------|------------------------------------------------------------------------------------------------------------------------------------|

| ADM      | it is essential for efficiently performing system administration procedures                                                        |

| ENGY     | it enables energy efficient operation of the system                                                                                |

| INFRA    | it is necessary to operate the system in the LRZ infrastructure                                                                    |

| PERF     | it is essential for achieving high application performance on the system                                                           |

| POL      | it is a prerequisite for adhering to LRZ's long term goal, management policies, and procedures                                     |

| PROJ     | it is necessary to assure timely conclusion of project milestones                                                                  |

| REL      | it is a prerequisite for reliable and stable operation of the system                                                               |

| STD      | users or administrators expect that the functionality under consideration conforms to published or de facto standards              |

| SUPP     | support, maintenance and bug fixes are essential                                                                                   |

| ТЕСН     | the system must provide state-of-the-art HPC technology in the specified area to achieve the procurement goals                     |

| USER     | it is an essential component of the system's user interface and enables its efficient and correct operation as well as ease of use |

For more details on the evaluation procedure see the document "Decision Criteria and Benchmark Description SuperMUC-NG".

## **1.10** Checking of requirements

During the acceptance phase of the system the requirements will be checked primarily by the following methods.

| Method                                            | The acceptance procedure will be based on                                   |  |

|---------------------------------------------------|-----------------------------------------------------------------------------|--|

| DOC                                               | <b>DC</b> checking the supplied documentation of the requirement's features |  |

| FUNC                                              | performing a functionality test                                             |  |

| INSP inspection of a delivered hardware component |                                                                             |  |

| BENCH                                             | execution of benchmark programs for performance verification                |  |

## 1.11 Additional material

The following non-contained material is referenced in this document:

- Anschreiben SuperMUC-NG

- Bewerbungs- und Vertragsbedingungen SuperMUC-NG.

- The floor plans of the computer rooms.

- Decision Criteria and Benchmark Description SuperMUC-NG.

This material is provided as a separate set of documents in the procurement download area.

## 1.12 Glossary

This document makes use of the following terms:

Accelerator: Processing hardware to perform some calculations faster than possible on general-purpose <u>central processing units</u>, e.g. GPGPUs.

Accelerated node: A node containing general purpose processors as host processing units and one or more accelerators.

**Cluster Export Services (CES):** provides highly available file and object services to an IBM Spectrum Scale GPFS<sup>TM</sup> cluster by using Network File System (NFS), Object, or Server Message Block (SMB) protocols.

Combined Phases 1+2: see Phases 1+2.

**Compute Nodes:** That part of the system used for performing computations. May be one of **Thin Node, Large Shared Memory Node, Accelerated Node** or **Many-Core Node**.

**Core:** Portion of a Multi- or Many-Core Processor that contains execution units, registers and caches.

**CPU:** Central Processing Unit.

**Data Science Storage (DSS):** LRZ's storage cluster based on **IBM Spectrum Scale** for sharing large scientific data within the HPC ecosystem.

#### Fat Node: see Large Shared Memory Node.

**File system:** This term is not always used in strict technical sense throughout this document. It describes the collection of file storage for specific purposes and implementation (such as storage for users' HOME files).

**General purpose compute node:** In the context of this document, a self-contained unit of hardware each (logical or physical) core of which can execute the instruction sequence generated by a standard C, C++ or Fortran compiler from any standard-conforming source code without use of additional language directives. A broad range of applications should be available and can be run with decent performance. Furthermore, the expectation is that the physical socket encompassing such a node has a significant market share in the server market; this currently implies that many-core architectures are not considered general purpose.

GPGPU: General Purpose Computing on Graphics Processing Unit.

**HPC Project:** A container – usually connected to a UNIX group – that defines scope, resource assignment and duration of a scientific project via a refereeing process. The duration of such a project is typically limited to a few years.

### HPL: HIGH PERFORMANCE LINPACK Benchmark

**IOPS:** Refers to the I/O metadata operations per second supplied by a storage system down to a client.

**Island:** Refers to a group of nodes with the best interconnect network characteristics in the system (e.g. blocking factor, bandwidth, latency). Between islands, the network characteristics may be degraded. If the internal network has no hierarchical structure, then the term refers to just an arbitrary grouping of processors (e.g. for use within the benchmarking procedure).

**kByte, MByte, GByte, TByte** in the context of memory and cache mean  $10^3$ ,  $10^6$ ,  $10^9$ ,  $10^{12}$  Bytes. This also applies for memory/cache related bandwidths.

**kiByte, MiByte, GiByte, TiByte or PiByte** in the context of disk space mean  $2^{10}$ ,  $2^{20}$ ,  $2^{30}$ ,  $2^{40}$ ,  $2^{50}$  Bytes. These procurement documents explicitly use GiByte, TiByte etc. for capacity and bandwidth specifications (including benchmark metrics) in this context.

**Large Shared Memory Node:** Also termed **fat node**. A node that contains significantly more main memory than a standard "Thin" computational node.

Login Node: System that is deployed as a front end for user access.

Many-Core Node: A node which contains one or more many-core processors as central processing units

**Many-Core-Processor:** A multi-core processor architecture with a high number of cores (typically more than 60) sharing a random-access memory.

**Node:** Computer connected to the high-performance network interconnect running a single Linux OS instance. It contains a set of cores and possibly attached accelerator devices that share a random-access memory within the same memory address space.

**PGAS:** Partitioned Global Address Space, a parallel programming model.

Phase 1: Refers to goods and services delivered for the first installation phase (in 2018/19).

Phase 2: Refers to the additional goods and services delivered for the second phase.

**Phases 1+2:** Refers to aspects of the goods and services which are established through the combination of Phase 1 and Phase 2 (e.g. performance of an application that runs on the entire system)

**RAS:** Reliability, availability and serviceability.

**RDMA:** Remote Direct Memory Access. A network feature that enables efficient inter-node memory addressing.

**RFP:** Request for Procurement.

Server Node: A system used for management purposes.

SSD: Solid State Disk.

**SuperMUC-NG:** SuperMUC Next Generation.

**Thin Shared Memory Node:** A shared-memory node with two CPUs and a memory size typical for distributed memory HPC processing.

**Tenderer:** The company that submits this proposal and, if awarded the contract, is the sole general contractor for the SuperMUC-NG system (also: Vendor, Offeror)

VM: Virtual Machine (used in context of the Cloud component).

## 2 Project Management Requirements

## 2.1 Project Management

SuperMUC-NG will be a costly and complex system with significant technological risks and therefore requires professional project management during delivery, installation, system acceptance and early life support.

M 1: The Tenderer must assign a project manager and install a Project Management Office with at least one additional person to offload administrative tasks, ensure a "four-eyes" principle, and provide redundancy.

Check here that this requirement will be fulfilled:

I 1: The project manager should have previous installation experience with similar projects and hold a valid certification in project management (e.g. IPMA Level B or PMI PMP<sup>6</sup>).

Check here that this requirement will be fulfilled:

[]

[]

[ ]

The Tenderers' project manager will work together with LRZ's project manager. Main principles of this collaboration shall be documented in a shared project management plan.

The Tenderer is solely responsible for the main part of delivery and installation but LRZ requests continuous read access to relevant project management documentation. The goal is to make sure that any unclear requirements or problems can be addressed as early as possible and formal acceptance is not delayed unnecessarily.

M 2: The Tenderer must develop and submit a Project Management Plan and must manage the installation and commissioning of the system according to this Plan.

The following documents must be developed, actively maintained and made available to LRZ:

- Project Management Plan, including at least sub-plans for Scope, Schedule, Quality, Risk, Stakeholder, Communications<sup>7</sup> and Project Change Management

- Initial Project Milestone Plan

- Work Breakdown Structure<sup>8</sup>

- Schedule Baseline and Project Schedule<sup>9</sup>

- Risk register of the Tenderer

Check here that these requirements will be fulfilled:

<sup>&</sup>lt;sup>6</sup> See: <u>http://de.wikipedia.org/wiki/International\_Project\_Management\_Association</u>

<sup>&</sup>lt;sup>7</sup> Inhalts- und Umfangs-, Termin-, Qualitäts-, Risiko-, Stakeholder- und Kommunikationsmanagement.

<sup>&</sup>lt;sup>8</sup> Projektstrukturplan

<sup>&</sup>lt;sup>9</sup> Original- und tatsächlicher Terminplan

## I 2: The Tender should specify which industry standard is followed for the Project Management Plan (e.g., PMBoK, PRINCE2, PMI, etc.)

[Insert text here]

### 2.2 Risk Assessment

I 3: The Tenderer should comment on the following risks and their probability.

Although some of the risks are within the responsibility of LRZ, Tenderers are asked to provide their assessment and suggestions for possible countermeasures. For all items, a probability estimate of the form High, Medium or Low should be assigned.

I 4: For all items with an assigned probability estimate of Medium or High, a mitigation description should be supplied.

**The Tenderer or one of its main suppliers may cease operation** e.g. due to bankruptcy. In this case it may not be possible to deliver or operate the system or parts of it.

Comments and mitigation measures: [Insert text here]

The Tenderer or one of its main suppliers may run into financial instability. This may cause delays in the installation process. It may also reduce the availability of human staff on the Tenderers' or its suppliers' side.

Comments and mitigation measures: [Insert text here]

**Technology road maps may be considerably delayed or cancelled**, Tenderers or one of their suppliers cannot adhere to contracted time schedules e.g. because technical problems delay the availability of components or their interoperability. It may take considerable time to fix these technical problems.

Comments and mitigation measures: [Insert text here]

**Contracted technical properties may be not available**. The Tenderer or one of its suppliers cannot adhere to contracted technical properties. As can be seen from known issues with global parallel file systems this risk includes (system) software. It may take considerable time to fix these technical problems.

Comments and mitigation measures: [Insert text here]

**Unexpected failure of a large number of critical components due to previously unknown problems**. This includes defective motherboards, cables, failures of cooling components, etc. It may require extensive replacement programs.

Comments and mitigation measures: [Insert text here]

**Operational limits** (AC power, cooling, temperature) may be exceeded, or support budget may become overstrained.

Comments and mitigation measures: [Insert text here]

**Software scalability limits:** Software (e.g. OS, batch system, MPI, parallel file system etc.) may be not mature enough to scale with the size of the system, the number of jobs, etc.

Comments and mitigation measures: [Insert text here]

Although a system passes the acceptance test, it may not be reliable enough for long program runs. Possible causes may be insufficient node reliability, insufficient reliability of the communication network or insufficient reliability of the I/O subsystem (most likely for shared global file systems), frequent disk failures or defect batches of cables or connectors. Our experience with previous systems indicate a **medium to high probability** that such issues will happen.

Comments and mitigation measures: [Insert text here]

**Applications do not compile or fail to execute as designed:** Examples are programs that do not compile/link and programs that produce wrong results. The main causes are compiler errors, library errors, CPU errors and errors in the communication hardware (including firmware) and communication software.

Comments and mitigation measures: [Insert text here]

**Applications suffer from unexpected performance degradation:** This may be related to the code generation of a compiler (e.g. an update), to a suboptimal implementation of library routines or missing optimized library routines for special purposes.

Comments and mitigation measures: [Insert text here]

**Tools** for performance analysis and debugging turn out to be **too unstable or immature for working on** large-scale applications.

Comments and mitigation measures: [Insert text here]

**Tax** increases (VAT) or the development of the **currency exchange rate** may make the Tenderer's calculations invalid.

Comments and mitigation measures: [Insert text here]

Qualified personnel is not available during the installation or the early life support phase or changes frequently.

Comments and mitigation measures: [Insert text here]

## Other simultaneous installation projects of the Tenderer divert resources and/or qualified personnel from the SuperMUC-NG project.

Comments and mitigation measures: [Insert text here]

### Key personnel in the project becomes unavailable.

Comments and mitigation measures: [Insert text here]

Please describe **additional risks** which appear significant, assess these risks, where applicable and describe potential countermeasures.

Comments and mitigation measures: [Insert text here]

## **3** Requirements for SuperMUC-NG

## **3.1 Installation requirements**

The Tenderer's proposal for installation must ensure that the offered system is physically installable and operable, and it must allow a reliable and comprehensible prediction of air conditioning, cold and warm water cooling demands, and energy consumption.

### **3.1.1** Proposal for installation

M 3: A technical proposal for the installation for both phases must be provided.

The proposal must include the following items:

- A detailed space assignment plan for Phase 1 (including rack layout draft) and a conceptual plan for a potential Phase 2

- Cabinet dimensions, packaging diagrams, weights (in all configurations in packaging, dry, with any liquid coolant) and electrical requirements

- Raised floor requirements and cutouts

- Cable tray requirements

- Environmental requirements

- Expected AC power and cooling requirements

- Cooling water quality requirements

- Safety and health requirements

- I 5: This criterion has been converted to a mandatory one.

### M 3a:

Information about:

- the earliest and latest installation date of Phase 1

- the earliest installation date of Phase 2

- the time needed to complete the installations

- the length of interruption of service of Phase 1 needed for installation of Phase 2 must be submitted.

Table 1 with milestones, activities and dependencies must be provided.

| Milestone or activity                                                | Estimated dates and major dependencies | Latest Date |

|----------------------------------------------------------------------|----------------------------------------|-------------|

| Site preparation and installation plan                               |                                        |             |

| Data Science Storage<br>delivered, installed and<br>accepted         |                                        |             |

| Phase 1 Test system<br>(incl. management)<br>delivered and installed |                                        |             |

| Phase 1 system<br>management core<br>components<br>delivered and installed                                 |  |

|------------------------------------------------------------------------------------------------------------|--|

| Phase 1 delivery of main hardware                                                                          |  |

| Phase 1 of previous LRZ<br>supercomputer is<br>decommissioned and site<br>is available for<br>installation |  |

| Site preparation by vendor                                                                                 |  |

| Phase 1 system<br>installation                                                                             |  |

| System Readiness<br>("Betriebsbereitschaft")                                                               |  |

| Date for acceptance of<br>Phase 1                                                                          |  |

| Estimated start of installation of Phase 2                                                                 |  |

**Table 1**: System installation milestones, activities and dependencies.

[Insert text here]

### 3.1.2 Site Preparation and Installation Plan

| I 6: | Not later than three months after signing of the contract, the Tenderer should<br>Site Preparation and Installation Plan. This plan will be updated as necessary<br>performance of the contract and will be subject to perusal and approval by L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | / during |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | <ul> <li>The plan should cover at least the following items:</li> <li>Cabinet dimensions, packaging diagrams, weights (in all configurations –<br/>in packaging, dry, with any liquid coolant) and electrical requirements</li> <li>System layout and cabling requirements, including expansion options</li> <li>Raised floor requirements and cutouts</li> <li>Cable tray requirements</li> <li>Environmental requirements</li> <li>Expected AC power and cooling requirements</li> <li>Cooling water quality requirements</li> <li>Safety and health requirements</li> <li>Equipment delivery schedule</li> <li>Staging and temporary storage area needs</li> <li>Pre-delivery access and work needs</li> <li>Shipping plans</li> <li>Equipment layout and installation sequence (for multi-stage deliveries)</li> <li>Bring-up plan</li> <li>Quality Assurance plan</li> </ul> |          |

|      | - Verification and Validation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

|      | Check here that this requirement will be fulfilled:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | []       |

[Insert text here]

### **3.1.3 Installation Locations**

The compute part of the offered system shall be installed in the HRR<sup>10</sup> computer room of the LRZ data centre building; for other parts of the offered system different rooms are targeted. The building has two **freight elevators** with the following clearance dimensions:

Freight elevator on the west side of the building:

- width x depth x height =  $1,95m \times 2,95m \times 2,58m$

- maximum payload = 3000 kg

Freight elevator on the east side of the building:

- width x depth x height =  $1,60m \ge 2,40m \ge 2,30m$

- maximum payload = 2000 kg

In order to enable a transport of the system components to the designated computer room in the third floor, all system components shall not exceed the following dimensions:

• width x depth x height =  $1,60m \ge 1,60m \ge 2,58m$  for cubic based components, or

<sup>&</sup>lt;sup>10</sup> Höchstleistungs-Rechner-Raum

- width x depth x height =  $1,20m \ge 2,50m \ge 2,58m$  for very deep components

- width x depth x height =  $2,50m \times 1,20m \times 2,58m$  for very wide components

The floor plan of the designated computer room of LRZ is included with the tender documents. This room is reserved for Phase 1 and Phase 2 of SuperMUC-NG; it is free of pillars and has the following dimensions and false floor specifications:

- width x depth x height =  $52,5m \times 21m \times 8m (= 1102,5m^2 \times 8m)$

- false floor with a maximum area load of 1500 kg per m<sup>2</sup> (~ 15 kN/m<sup>2</sup>), a maximum "*point load*" of 500 kg (5 kN) and a height of 1.8m

After shutdown and decommissioning of SuperMUC Phase 1 the facilities used by SuperMUC Phase 1 will be available for the installation of SuperMUC-NG Phase 1.

After shutdown and decommissioning of SuperMUC Phase 2 the facilities used by SuperMUC Phase 2 will be available for the installation of SuperMUC-NG Phase 2.

A floor plan containing details of this area is included in the tender documents.

### M 4: Note – this requirement has been modified:

The transportation of the offered system (this includes Phase 1 and Phase 2) to the place of installation must be feasible under the constraints mentioned above.

The bulk of the compute part of Phase 1 of the offered system must be installable in the currently free area of the HRR computer room. This includes the constraints for floor space, power and cooling, maintenance areas. If the area or point load constraints are violated, the necessary reinforcements for the false floor and the transportation path must be part of the offer.

By checking the box, the Tenderer also declares that the complete installation process and preparation for operation of the system (for both installation phases) is incumbent on the Tenderer<sup>11</sup>.

Check here that this requirement will be fulfilled:

[]

If the offer for the compute nodes does not fit completely into the currently free area, it may be possible to supply additional space for it by removing the southernmost two rows of SuperMUC phase 1 compute nodes somewhat earlier than end of 2018.

M 4a Note - new Requirement:

The Tenderer must indicate whether this additional area (and how much of it) will be needed, and when it will be needed.

Some components of the system (in particular, see sections 3.5.8 and 3.14.2) should be installed one floor level lower, in the NSR0 or NSR1 computer rooms. The following table provides an overview of the facilities available there:

<sup>&</sup>lt;sup>11</sup> LRZ only lends the necessary technical support.

| Room                                | NSR0                        | NSR1             |

|-------------------------------------|-----------------------------|------------------|

| False floor height (cm)             | 80                          | 80               |

| Available area                      | Rows 2 and 3 north, 15 rack | No restrictions  |

|                                     | units per row               |                  |

| Max. area load (kN/m <sup>2</sup> ) | 15                          | 15               |

| Max. point load (kN)                | 5                           | 5                |

| Air cooling capacity (kW)           | 400                         | 50 (dehydration) |

| Cold water cooling capacity         | 2 x 300 (south/north)       | 360              |

| (kW)                                |                             |                  |

| Electrical power (kW)               | 800                         | 800              |

For NSR0, the supplied floor plan indicates where SuperMUC-NG related hardware can be installed.

[Insert text here]

### **3.1.4** Conformity with electrical standards

LRZ provides power supply of 50 Hz alternating current, with 230 V single-phase and 400 V three-phase voltages, as commonly available in Germany. LRZ provides 175 power distribution boxes in the false floor for the electrification of the system, each containing two IEC 60309 32 Ampere five-pole, three-phase power connectors.

M 5: The required connectors, frequency or voltage transformers must be included in the tender in case that other electrical power connectors or other electrical power characteristics are needed.

The installation costs for such components is part of the contract and must not be charged separately.

Check here that this requirement will be fulfilled: []

The *EC Directive on Electromagnetic Compatibility of Devices* is the guideline for all manufacturers, importers, and distributors of electric and electronic devices in the European Union as far as development, production and distribution of devices, systems and equipment are concerned. In addition, the *Low-Voltage Directive 2014/35/EU* and the *Act about Product Liability* must be considered. These regulations and the corresponding directives and standards are EU stipulations that have been adopted by German Law. By attaching a "CE marking" on a device, the manufacturer gives a legally binding declaration that the device conforms to all EMC relevant directives and standards of the EU and with the regulations and laws.

M 6: The system and its components must conform to German and European directives and laws at the time of delivery.

All necessary documentation must be submitted to LRZ before delivery of the system.

Check here that this requirement will be fulfilled: []

[Insert text here]

### 3.1.5 Power supply

The usage of highly energy efficient cooling technologies and all other aspects leading to a high Data Center Infrastructure Efficiency (DCIE) is an important goal of the SuperMUC-NG procurement. In this spirit, aspects such as free cooling and a possible use of waste heat to heat the LRZ buildings as well as possible use of waste heat to operate adsorption chillers are important and will be honored respectively.

M 7: The expected AC power draw of the offered system in normal user mode and the expected AC power draw of the system running the HPL benchmark must be specified.

The appropriate fields in the tables in Section 4 of this document must be filled in.

I 7: The total electrical AC power requirement of Phase 1 of SuperMUC-NG under HPL load should not exceed 5500 kW.

This does not include the additional AC power needed for the cooling of the system and the compute room.<sup>12</sup>

Check here that this requirement will be fulfilled:

[]

[]

I 8: The total electrical AC power requirement of the combined Phases 1+2 of SuperMUC-NG under HPL load should not exceed 7150 kW.

This does not include the additional AC power needed for cooling of the system and the compute room.

Check here that this requirement will be fulfilled:

If any of the above two requirements cannot be fulfilled, the provisioning of additional electrical AC power must be discussed.

T 1: It is desired that redundantly powered critical components (e.g. management servers, storage servers, and network components) are supplied via connections to different power bars.

Check here that this requirement will be fulfilled:

[Insert text here]

### 3.1.6 Cooling

To reduce cost and to improve energy efficiency, a major goal of LRZ is to use free cooling to as large as possible extent for the cooling of its HPC infrastructure. Hence, two distinct water cooling loops called Loop 1 and Loop 2, operating at different temperature levels will be available for the cooling of the system. The cooling loops will use the following water temperatures:

$<sup>^{12}</sup>$  cf. "Anschreiben SuperMUC-NG "

Loop 1:  $T_{in}=18^{\circ}C$ ;  $T_{out}=24^{\circ}C$ ;  $\Delta T=6K$ ; Loop 2:  $35^{\circ}C \leq T_{in} \leq 45^{\circ}C$ ;  $\Delta T \geq 6K$  (LRZ can only guarantee that throughout the year  $T_{in}$  does not exceed  $45^{\circ}C$ );

Here  $T_{in}$  denotes the water inlet temperature to the compute racks and  $T_{out}$  denotes the preferred water temperatures at the outlet side of the racks. Throughout the year, the maximum cooling power of these loops is

#### Loop 1: 1.3 MW Loop 2: 8.0 MW.

Due to its high inlet temperature, Loop 2 is operated **without any chillers** only using the free cooling capacities at the roof of the building. Loop 1 and Loop 2 are closed internal cooling loops, separated by heat exchangers (Loop 2) and mechanical chillers (Loop 1) from the glycol water cooling loops connected to the cooling towers at the roof of the building.

The water within these internal loops contains no glycol and only small amounts of additives such as corrosion inhibitors and biocides are to be expected according to VDI 2035<sup>13</sup>.

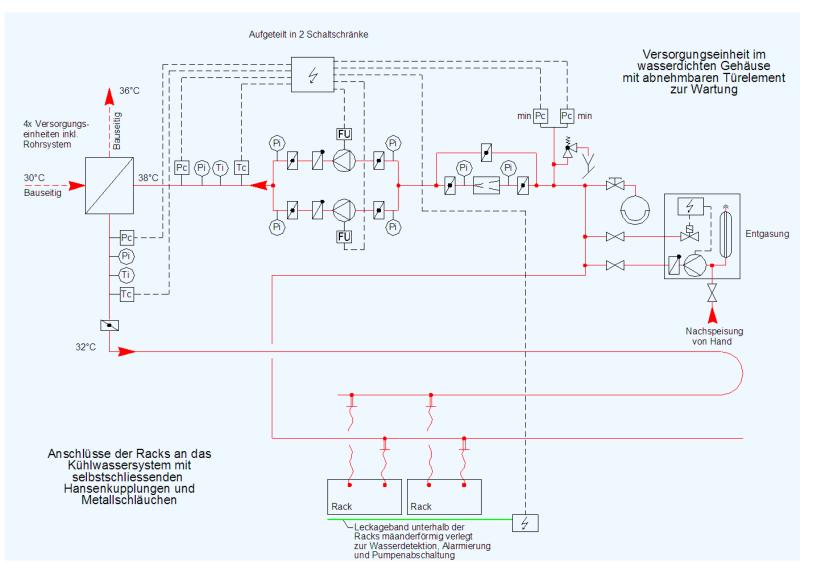

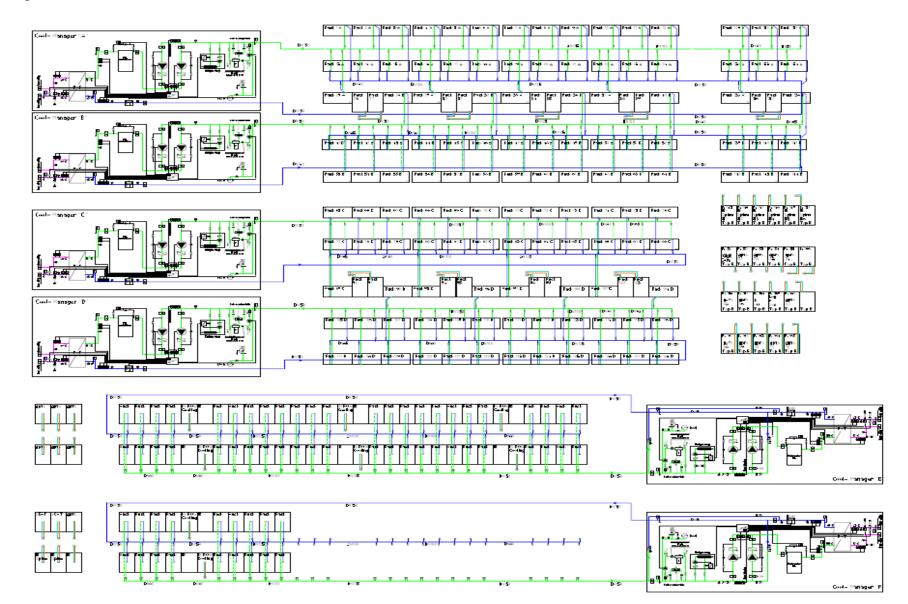

For direct cooling of IT equipment, a total of 5 stainless steel heat exchangers with accumulated heat transfer capacity of up to 6 MW are in use. Each unit is equipped with pressure, volume flow and temperature control unit, redundant water pumps and very fine grained filters (50  $\mu$ m) are installed in the HRR-room. The system setup of these so-called CooLManagers is shown in Figure 1. The Tichelmann Cooling Loops of SuperMUC Phase 1 and Phase 2 are shown in Figure 2.

M 8: In case the existing Tichelmann Cooling Loops cannot be reused, the Tenderer must deliver and install the warm water cooling supply lines for SuperMUC-NG Phase 1 and Phase 2.

Check here that this requirement will be fulfilled:

The operation points and maximum volume flows of the CoolManagers are listed below.

CoolManager A + B:

- Operating point: 115 m<sup>3</sup>/h (pumping head 23.4 mWS)

- Pumping head for 126 m<sup>3</sup>/h: approx. 22 m (2.2 bar)

CoolManager C + D:

- Operating point: 86.3 m<sup>3</sup>/h (pumping head 18.5 mWS)

- Pumping head for 126 m<sup>3</sup>/h: approx. 14 m (1.4 bar)

CoolManager E:

- Operating point: 143 m<sup>3</sup>/h (pumping head 20.4 mWS)

- Pumping head for 180 m<sup>3</sup>/h: approx. 14 m (1.4 bar)

CoolManager F:

- Operating point: 134 m<sup>3</sup>/h (pumping head 21.4 mWS)

- Pumping head for 180 m<sup>3</sup>/h: approx. 14 m (1.4 bar)

[]

<sup>&</sup>lt;sup>13</sup> See <u>https://www.vdi.de/technik/fachthemen/bauen-und-gebaeudetechnik/fachbereiche/technische-gebaeudeausruestung/richtlinienarbeit/vdi-2035/</u>

Figure 1: CooLManager hydraulic system

Figure 2: Tichelmann Cooling Loops of SuperMUC Phase 1 and Phase 2

LRZ operates a BACnet/IP building automation system by Johnson Controls to monitor its cooling infrastructure. In case a critical component of the cooling infrastructure fails, a 24/7 on-call technician can be notified by the building automation to take action.

M 8a: Note – new requirement:

Any cooling infrastructure that is going to be installed by the Tenderer and which is critical for operating SuperMUC-NG must be connected to LRZ's BACnet/IP network and integrated into the building automation system. The integration will be the duty of the Tenderer and must allow for monitoring the operational parameters and the status of this cooling infrastructure.

Check here that this requirement will be fulfilled:

[]

M 9: The type of cooling system for all devices (air-cooling, water-cooling, etc.) and details about the cooling system (e.g. in- and outlet temperature, temperature variation tolerance, pressure, purity requirements, etc.) and the required environmental conditions (e.g. ambient temperature, humidity, dust free conditions, etc.) must be specified.

In addition, the appropriate fields in the tables in Section 4 must be filled in.

M 10: The heat emission of all devices of the offered system, broken down into air and water cooling, i.e. the maximum values and estimated values for permanent load, must be specified.

Also the heat emission released into each of the two separate water cooling loops "Loop 1" and "Loop 2" must be specified.

In addition, the appropriate fields in the tables in Section 4 must be filled in.

I 9: The heat emission released into the **room air** should not exceed 120 kW for Phase 1 and 200 kW for Phase 1 and Phase 2.

Pease note that the air handlers for room air conditioning are connected to Loop 1.

Check here that this requirement will be fulfilled:

I 10: At least 97 % of the waste heat of the compute node racks should be removed by means of direct water cooling of the components with cooling Loop 2 under the following environmental circumstances:

Loop 2: T<sub>in</sub>=40°C ambient room temperature: 25°C

Check here that this requirement will be fulfilled:

I 11: The total heat emission of SuperMUC-NG Phase 1 released into the water cooling loop called Loop1 (chilled water cooling loop) should not exceed 0.8 MW.

Check here that this requirement will be fulfilled:

[]

[]

| I 12: The heat emission released into the water cooling loop called Loop 2 in normal mode should not exceed 4.0 MW in Phase 1 (warm water cooling loop). |                                                     | ormal user |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------|