Leibniz-Rechenzentrum

der Bayerischen Akademie der Wissenschaften

**Technischer Bericht**

Description of Goods and Services for the next Supercomputer in Bavaria (HLRB II)

Reinhold Bader, Matthias Brehm, Ralf Ebner, Helmut Heller, Herbert Huber, Hans-Ulrich Schäfer, Horst-Dieter Steinhöfer, Frank Wagner

#### Okt 2004

Direktorium:

Prof. Dr. H.-G. Hegering (Vorsitzender) Prof. Dr. A. Bode Prof. Dr. Chr. Zenger Leibniz-Rechenzentrum Barer Straße 21 D-80333 München

UST-ID-Nr. DE811305931

Telefon:

(089) 289-28784

Telefax:

(089) 2809460

E-Mail:

lrzpost@lrz.de

Internet:

http://www.lrz.de

U2, U8: U3, U4, U5, U6: Tram 27:

Königsplatz : Odeonsplatz Karolinenplatz

LRZ-Bericht 2004-04

Öffentl. Verkehrsmittel:

| 1 | Gen | eral info      | ormation on the RFP                                                    | 1  |

|---|-----|----------------|------------------------------------------------------------------------|----|

|   | 1.1 | Genera         | al objectives for the HLRB II                                          | 1  |

|   | 1.2 | Catego         | prization of the requirements for the HLRB II                          | 3  |

|   | 1.3 | Termin         | nology                                                                 | 3  |

|   | 1.4 | Requir         | rements with respect to the content of the tender                      | 3  |

|   | 1.5 | Additi         | onal material                                                          | 4  |

| 2 | Req | uiremen        | its for the HLRB II                                                    | 5  |

|   | 2.1 |                | ation requirements                                                     |    |

|   | 2.1 | 2.1.1          | Proposal for installation                                              |    |

|   |     | 2.1.1          | Date of Installation                                                   |    |

|   |     | 2.1.2          | Delivery to the place of installation                                  |    |

|   |     | 2.1.3          | Installation of the system                                             |    |

|   |     | 2.1.5          | Power supply and conformity with electrical standards                  |    |

|   |     | 2.1.6          | Environmental conditions                                               |    |

|   |     | 2.1.7          | Fire detection and protection                                          |    |

|   | 2.2 |                | •                                                                      |    |

|   | 2.2 |                | vare of the compute nodes                                              |    |

|   |     | 2.2.1          | Compute node architecture                                              |    |

|   |     | 2.2.2          | Performance of the SMP compute nodes                                   |    |

|   |     | 2.2.3          | Extent of inhomogeneity of installation Phases 1 and 2                 |    |

|   |     | 2.2.4          | Size of main memory                                                    |    |

|   |     | 2.2.5          | Bandwidth of main memory                                               |    |

|   |     | 2.2.6          | Memory and cache hierarchy                                             |    |

|   |     | 2.2.7          | Memory protection and error detection                                  |    |

|   |     | 2.2.8          | Hardware support of parallelization                                    | 12 |

|   | 2.3 | Comm           | nunication network                                                     | 12 |

|   |     | 2.3.1          | Hardware of internal interconnect                                      | 12 |

|   |     | 2.3.2          | Interconnect within Phase 1 or within Phase 2                          |    |

|   |     | 2.3.3          | Interconnect between Phase 1 and Phase 2                               |    |

|   |     | 2.3.4          | Control network                                                        | 14 |

|   |     | 2.3.5          | Connection to external network                                         | 14 |

|   | 2.4 | Diek e         | torage                                                                 | 15 |

|   | 2.4 |                | -                                                                      |    |

|   |     | 2.4.1          | User disk storage                                                      | 15 |

|   |     | 2.4.2          | Disk storage containing the operating system, swap and/or paging space | 10 |

|   |     | 242            | of the nodes                                                           |    |

|   |     | 2.4.3          | I/O nodes                                                              |    |

|   |     | 2.4.4          | Management tools for the disk subsystem                                | 1/ |

|   | 2.5 | Hardw          | vare faults                                                            | 17 |

|   |     | 2.5.1          | Detection of hardware faults                                           | 17 |

|   |     | 2.5.2          | Mean time between failures                                             | 18 |

|   | 2.6 | Operat         | ting system                                                            | 18 |

|   | 2.0 | •              |                                                                        |    |

|   |     | 2.6.1<br>2.6.2 | 64-bit operating system                                                |    |

|   |     | 2.6.2<br>2.6.3 | Standards                                                              |    |

|   |     | 2.6.5          | Checkpointing                                                          |    |

|   |     | 2.6.5          | Job freeze                                                             |    |

|   |     | 2.0.5          |                                                                        |    |

|      | 2.6.6   | Workload management (WLM)                                            | . 20 |

|------|---------|----------------------------------------------------------------------|------|

|      | 2.6.7   | Operating System induced scheduling noise                            | 20   |

|      | 2.6.8   | Gang scheduling                                                      | 21   |

|      | 2.6.9   | Support for large pages                                              | 21   |

| 2.7  | Batch r | processing                                                           | 21   |

|      | 2.7.1   | Batch scheduling system                                              |      |

|      | 2.7.2   | Job surveys                                                          |      |

|      | 2.7.2   | Coexistence of batch and interactive mode                            |      |

|      | 2.7.3   | Co-scheduling and resource reservation                               |      |

|      |         |                                                                      |      |

| 2.8  | Admin   | istration                                                            |      |

|      | 2.8.1   | User administration                                                  |      |

|      | 2.8.2   | User validation                                                      |      |

|      | 2.8.3   | System prologues                                                     |      |

|      | 2.8.4   | Security                                                             | . 25 |

|      | 2.8.5   | Secure Shell                                                         | 25   |

|      | 2.8.6   | Configuration files                                                  | 25   |

| 2.9  | Data H  | andling                                                              | 25   |

|      | 2.9.1   | File systems                                                         |      |

|      | 2.9.2   | Archive and backup                                                   |      |

|      | 2.9.3   | Hierarchical storage management                                      |      |

|      | 2.9.4   | AFS                                                                  |      |

| 2 10 | Monito  | ring                                                                 | 27   |

| 2.10 | 2.10.1  |                                                                      |      |

|      |         | Verification of system configuration                                 |      |

|      |         | Log files                                                            |      |

|      |         | Multilevel administration rights                                     |      |

|      |         | Status of operating system                                           |      |

|      |         | Operating system errors                                              |      |

|      |         | Operator interface                                                   |      |

|      |         | Operation surveys                                                    |      |

| 0.11 |         |                                                                      |      |

| 2.11 | •       | tuning and testing                                                   |      |

|      |         | Tuning of the operating system and performance monitoring            |      |

|      | 2.11.2  | Test versions of software                                            | 30   |

| 2.12 | System  | restarts and upgrades                                                | 30   |

|      | 2.12.1  | System restarts                                                      | 30   |

|      | 2.12.2  | Modifications of the operating system                                | 30   |

|      | 2.12.3  | Operating system upgrade                                             | 31   |

| 2.13 | Softwa  | re                                                                   | 31   |

| 2.13 |         | Compilers                                                            |      |

|      |         | Features of the compilers                                            |      |

|      |         | Third party compilers, libraries and development tools               |      |

|      |         | Other parallel compilers and tools                                   |      |

|      |         | Message passing                                                      |      |

|      |         | Other message passing libraries                                      |      |

|      | 2.13.0  |                                                                      |      |

|      | 2.13.7  | •                                                                    |      |

|      |         | Performance analysis, profiling, and hardware performance monitoring |      |

|      |         | Parallel programming environment                                     |      |

|      |         | Third Party Software                                                 |      |

|      |         | 2 Shells and scripting languages                                     |      |

|      |         | 3 GNU development tools                                              |      |

|      |         |                                                                      | 20   |

|   | 2.14 | Trainin        | g, user support and technical support                                                                                                     |    |

|---|------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------|----|

|   |      | 2.14.1         | Documentation                                                                                                                             |    |

|   |      | 2.14.2         | Introduction to the system                                                                                                                |    |

|   |      |                | User support                                                                                                                              |    |

|   |      |                | System-related support                                                                                                                    |    |

|   | 2.15 | Mainte         | nance                                                                                                                                     | 40 |

|   | 2.15 |                | Hardware maintenance                                                                                                                      |    |

|   |      |                | Software maintenance                                                                                                                      |    |

|   |      |                | Total cost of maintenance                                                                                                                 |    |

|   |      |                |                                                                                                                                           |    |

|   | 2.16 | Collabo        | pration with the vendor                                                                                                                   | 41 |

| 3 | Benc | hmarkiı        | ng procedure for the HLRB II                                                                                                              | 43 |

|   | 3.1  | Overvie        | ew of the benchmarking procedure                                                                                                          | 43 |

|   |      | 3.1.1          | Confidentiality                                                                                                                           | 43 |

|   |      | 3.1.2          | Code modifications                                                                                                                        | 44 |

|   |      | 3.1.3          | Hints for optimization                                                                                                                    | 44 |

|   |      | 3.1.4          | Limitations of optimization                                                                                                               | 44 |

|   |      | 3.1.5          | Implementation of basic data types                                                                                                        |    |

|   |      | 3.1.6          | Conversion of timing to performance values                                                                                                |    |

|   |      | 3.1.7          | Rules for systems which are not available for benchmarking                                                                                |    |

|   |      | 3.1.8          | Failure to reach the required minimum performance values                                                                                  |    |

|   |      | 3.1.9          | Commitments for installation Phase 1 and 2                                                                                                |    |

|   |      | 3.1.10         | Disclosure by the vendor and submission of results to LRZ                                                                                 | 46 |

|   |      | 3.1.11         | Disclosure of the optimizations to the authors of the benchmarks                                                                          | 46 |

|   |      | 3.1.12         | Delivery of the benchmark sources by LRZ                                                                                                  | 46 |

|   | 3.2  | Aggreg         | ate computing performance                                                                                                                 | 47 |

|   | 3.3  | Infrastr       | ucture for the benchmark suite                                                                                                            | 49 |

|   |      | 3.3.1          | Setting up the source tree                                                                                                                | 49 |

|   |      | 3.3.2          | Low-level library used by the benchmark programs                                                                                          | 49 |

|   |      | 3.3.3          | Building an executable                                                                                                                    |    |

|   |      | 3.3.4          | Running a benchmark executable                                                                                                            | 50 |

| 4 | Bono | hmarka         |                                                                                                                                           | 51 |

| - | Dene | iiiiai Kõ      |                                                                                                                                           |    |

|   | 4.1  | Interco        | nnect-related benchmarks                                                                                                                  | 51 |

|   |      | 4.1.1<br>4.1.2 | MPI-1 Benchmark: Link bandwidth of a node, one MPI task per node<br>MPI-1 Benchmark: Saturated link bandwidth and interconnect balance of | 51 |

|   |      | 1.1.2          | a node                                                                                                                                    | 52 |

|   |      | 4.1.3          | MPI-1 Benchmark: Bisection bandwidth and latency within a Phase                                                                           |    |

|   |      | 4.1.4          | MPI-1 Benchmark: Bisection bandwidth and latency between Phase 1                                                                          |    |

|   |      | 4.1.5          | and Phase 2<br>MPI-2 Benchmark: Bisection bandwidth for one-sided communication                                                           | 56 |

|   |      |                | within a Phase                                                                                                                            | 58 |

|   | 4.2  | Storage        | e subsystem benchmarks                                                                                                                    |    |

|   |      | 4.2.1          | IOBench 1: multi-stream read/write for SAN/DAS storage subsystem                                                                          |    |

|   |      | 4.2.2          | IOBench 2: multi-stream read/write for NAS storage subsystem                                                                              |    |

|   |      | 4.2.3          | MPI-IO Benchmark                                                                                                                          |    |

|   |      | 4.2.4          | Metadata Benchmark                                                                                                                        | 64 |

|   | 4.3  | Kernel         | Benchmarks                                                                                                                                | 65 |

|   |      |                | RINF1                                                                                                                                     |    |

|   |      |                | · · · · · · · · · · · · · · · · ·                                                                                                         |    |

|   |      | 4.3.2    | FFT                                                     |    |

|---|------|----------|---------------------------------------------------------|----|

|   |      | 4.3.3    | SipSolver                                               |    |

|   |      | 4.3.4    | ZHEEVD                                                  | 74 |

|   |      | 4.3.5    | DMRG                                                    | 75 |

|   |      | 4.3.6    | Laser                                                   | 77 |

|   |      | 4.3.7    | LINPACK                                                 |    |

|   | 4.4  | Applic   | ation Benchmarks                                        | 80 |

|   |      | 4.4.1    | BEST                                                    | 80 |

|   |      | 4.4.2    | BQCD                                                    |    |

|   |      | 4.4.3    | Cactus                                                  |    |

|   |      | 4.4.4    | HEPFP                                                   |    |

|   |      | 4.4.5    | MGLET                                                   |    |

|   |      | 4.4.6    | NWChem                                                  | 89 |

| 5 | Benc | hmark    | Evaluation                                              |    |

|   | 5.1  | Weigh    | ted overall performance of Phase 1                      |    |

|   | 5.2  | Overal   | 1 performance of Phase 2                                |    |

|   | 5.3  | Proced   | lure for ranking the performance of the offered systems |    |

|   | 5.4  | Qualita  | ative evaluation                                        |    |

| 6 | Tabl | e of key | system parameters                                       |    |

# 1 General information on the RFP

# **1.1 General objectives for the HLRB II**

The supercomputer to be acquired, "Höchstleistungsrechner in Bayern II" (HLRB II), will serve German universities and research institutions to carry out research that requires extremely high CPU performance, high bandwidths to and from memory, to remote nodes and to disks, large main memory, and large disk storage capacity.

In its concept for the HLRB II, LRZ starts out from the assumption that the realization of coarse granular parallelization is easier and more efficient with a moderate number of high-performance nodes than with a large number of low-performance nodes. Therefore, MPP-like systems with many thousands of nodes with a relatively low individual performance - this includes workstation or PC clusters - will not be accepted for the planned system.

Additionally, the experiences with the current supercomputer show that many users utilize the hybrid programming model with MPI between the compute nodes and autoparallelization or OpenMP within the nodes.

Examples of computers that have the required characteristics include clusters with high-performance SMP-nodes (with 8 or more CPUs per node) or clusters of parallel vector processors (PVP). Many of the programs intended for execution on the new system, but not all, contain fine and medium grained parallelism and are also vectorizable. Therefore the system should be capable of efficiently processing programs via automatic fine and automatic medium grained parallelization within the SMP node and optionally via vectorization or vector-like techniques.

As mentioned before, the message passing paradigm will be used for coarse grained parallelism. As a consequence, the system must be equipped with a very efficient internal interconnect as well as an MPI implementation that makes optimal use of the hardware for communication between the nodes.

In order to achieve the highest possible level of performance, it will be necessary to exploit parallelism at all levels of a program, i.e., coarse grained parallelism at the level of domain decomposition, parallelism at the level of outer loops, and optionally vector-like parallelism at the level of inner loops. Thus, the objective of the HLRB II concept is to provide an environment offering a connection between coarse grained parallelization by domain decomposition, inevitable to achieve high performance, and the other two parallelization levels.

The following programming paradigms for parallelization should be available:

- Pure MPI Mode: message passing (+ optionally vectorization)

- Hybrid/Mixed Mode: message passing + shared memory (auto)parallelization/OpenMP (+ optionally vectorization).

In case that the performance of a single SMP node is powerful enough, the

• Pure Shared Memory Mode: (auto)parallelization/OpenMP (+ optionally vectorization)

is welcome by many users as an easy-to-use method. However, because of the generally limited scaling behavior of this mode, evaluation of the system is primarily based on the first two modes.

Experience and theoretical considerations show that for achieving optimal performance with the hybrid mode, a fully thread-safe implementation of MPI is essential.

The software necessary and commonly used for scientific and technical high-performance computing must be available (a UNIX or Linux operating system suitable for supercomputing centers, highly efficient compilers, libraries, tools, ISV applications).

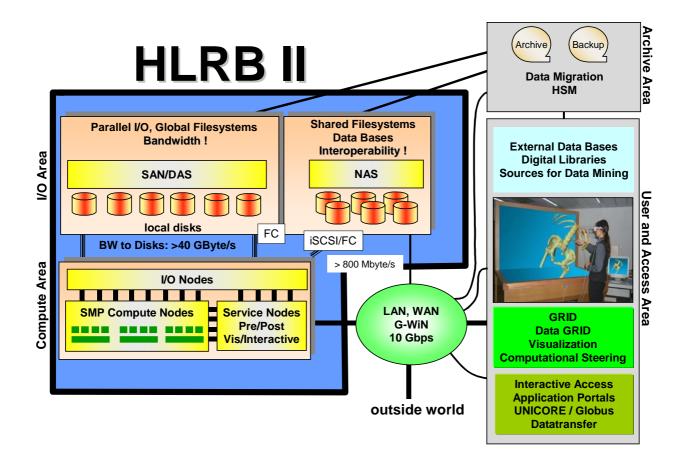

Together with the compute nodes, the vendor must offer a sufficiently large and efficient mass storage subsystem for user data. The user storage sould be subdivided into two parts:

- a huge SAN/DAS part (Storage Area Network or Direct Attached Storage) which should contain the large user results files and temporary data. For these data high bandwidth and moderate access latencies are required.

- a NAS part (Network Attached Storage) for permanent user data, such as source files and input data. The size of the individual files will be moderate but the number of files will be high. Access latencies should be low, while bandwidth for the NAS part should be moderate. The NAS part should also be accessible from outside the HLRB II.

In addition to that, disks for the operating system, paging and/or swapping, etc. may be required.

Furthermore, the vendor should offer an efficient external communication network connection for access to the HLRB II from the German research network.

The expected job profile on the HRLB II requires, simultaneously, high computing performance, a large main memory with fast access characteristics, an efficient interconnect, and high I/O throughput. Therefore, it is most important that the offered supercomputer provides a balanced configuration of hardware and software.

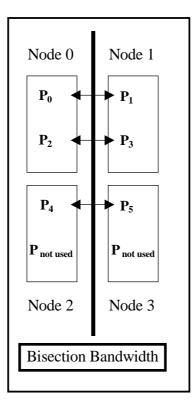

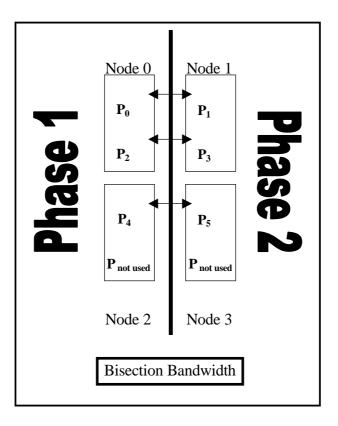

The installation of the HLRB II shall be accomplished in two phases:

- In Phase 1, starting at the end of 2005, 50 percent of the system resources should be installed.

- In Phase 2, starting in mid 2007, the rest of the system shall be installed.

Due to the fact that programs will have long run times, the offered HLRB II has to ensure high stability under permanent load with changing usage profiles.

Even in the first installation phase, the intended system should have the appropriate resources to achieve one of the upper positions among supercomputers worldwide.

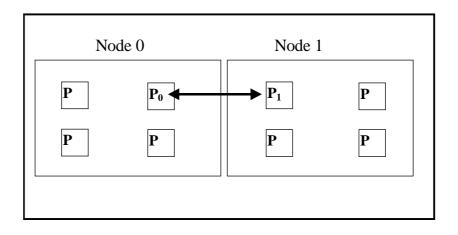

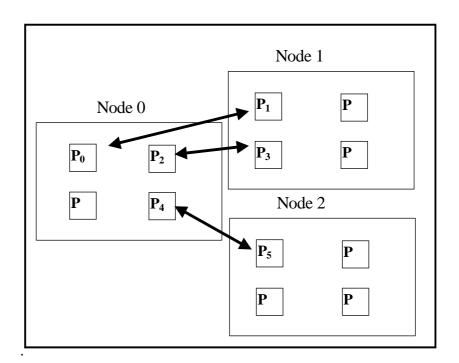

The general concept of the systen is depicted in the following Figure. Only the area surrounded by the broad black line is subject of the present procurement.

# 1.2 Categorization of the requirements for the HLRB II

The detailed list of requirements given below for the HLRB II are categorized within this document by three classes which are marked by colored boxes:

M Requirements within red boxes and marked by "M" are considered **mandatory**. It will constitute an exclusion criterion if they cannot be satisfied by the offered system.<sup>1</sup>

All other requirements must be fulfilled in their meaning and intended spirit, ensuring the operability and usability of the HLRB II.

Requirements within yellow boxes and marked by "I" are considered **important** for the operation and usability of the system.

In case that one or more of these non-exclusionary requirements cannot be fulfilled by the vendor, alternative offers and proposals for alteration are explicitly allowed as long as they provide equivalent characteristics.

The proposed alternatives must be explained in detail.

However, excessive failure to satisfy the spirit of the requirements may also constitute an exclusion criterion, or these failures may lead to a qualitative devaluation in conformance with the evaluation procedure.

T Requirements within green boxes and marked by "T" are considered **targets** for optimal usage of the system. If a vendor can fulfill these requirements this will lead to a qualitatively better ranking through the evaluation procedure.

Many requirements contain checkboxes.

[ ] an empty checkbox means that the requirement cannot be fulfilled

**[X]** a checkbox marked by "x" means that the requirement can be fulfilled.

# 1.3 Terminology

The following terms are used in this document:

- **Phase 1:** refers to goods and services delivered for the first installation phase.

- Phase 2: refers to the additional goods and services delivered for the second phase.

- **Combined Phase 1+2:** refers to aspects of goods and services which can be rendered by the combination of Phase 1 and Phase 2 (e.g., performance of an application which runs on the entire system).

- **kByte, MByte, GByte or TByte** in the context of memory or cache means 2<sup>10</sup>, 2<sup>20</sup>, 2<sup>30</sup>, 2<sup>40</sup> Byte, resp. This also applies for memory/cache related bandwidths.

- **kByte, MByte, GByte or TByte** in the context of disk means 10<sup>3</sup>, 10<sup>6</sup>, 10<sup>9</sup>, 10<sup>12</sup> Byte, resp. This also applies to disk related bandwidths.

# **1.4** Requirements with respect to the content of the tender

Please explain in your tender how the given requirements can be fulfilled. All items mentioned in the following chapters must be covered.

<sup>&</sup>lt;sup>1</sup> cf. "Bewerbungs- und Vertragsbedingungen"

The answers should refer only to offered goods and services and their alternatives. Answers and explanations must be inserted in the appropriate sections of this document and should be as concise as possible. It is preferred that the vendor uses the provided fields which are labeled by:

Answers and annotations by the vendor:

#### [Insert text here]

Additionally, the table at the end of this document with the key hardware parameters of the system must be filled in for Phase 1 and where applicable and known for Phase 2 and/or for the combined Phases 1+2. The vendor is free to provide additional information at the end of any paragraph.

Questions that have not been answered or have been answered insufficiently will be considered as answered in the negative.

# Any difference between installation Phase 1 and Phase 2 must be explained in this description. Any description that does not explicitly refer to one of the installation phases is considered valid for both phases.

Wherever appropriate and possible, there should be references to common standards of information technology. Bibliographical references, also to brochures and manuals, are desirable, but can only be considered as supplementary information, i.e., they cannot replace the required answers or explanations.

The vendor may hand in the specifications stipulated below in German or English or a mixture of both.

# **1.5** Additional material

The following material is referenced in this document

- Specification of the new computer building

- CD containing the floor plan of the computer room, the benchmarks, this document as MS Word and PDF

# 2 Requirements for the HLRB II

The following chapter stipulates the technical requirements which the offered system needs to fulfil.

In many cases, there are, besides the requirements, additional questions which have to be answered. These questions will help to clarify facts relevant for the operation and usage of the offered HLRB II. The evaluation of the answers can result in a higher or lower ranking of the tender if the appropriateness of the system for operation as a national supercomputer seems to be particularly advantageous or disadvantageous when compared to the average of all tenders.

Aspects which will be evaluated include, but are not necessarily limited to:

- whether the configuration is balanced and therefore appropriate for the expected usage, with respect to the relevant values of

- CPUs, processors or nodes

- main memory

- mass storage

- internal interconnect, and

- connection to the external communication network

- the relative and absolute bandwidths and latencies of the memory hierarchy, of the interconnects, and of the I/O subsystem

- the size of the shared memory of a node

- the extend of inhomogeneity between Phase1 and Phase2

- the flexibility in job administration and management, and verification of usage within the ambit of the explained aims of operation

- the possibilities provided by the software to ensure high quality of usability, a well-balanced load distribution, and operational security for the expected application profile

- the expected stability of hard- and software and downtimes caused by error recovery or debugging

- the expected downtimes caused by software maintenance and upgrades of the operating system

- the quality and availability of compilers, debuggers, test aids, and tools for performance analysis

- the extent and availability of means for control and evaluation of usage patterns

- the extent and availability of optimized scientific libraries and applications

- the expected improvement of usage due to the quality of documentation

- the support of general HPC activities by the vendor

- quality of vendor support for the operation of the HLRB II

# 2.1 Installation requirements

The description of installation requirements ensures that the offered system is physically installable and operable. The specifications must allow a reliable prediction of air conditioning, cooling demands, and energy consumption.

#### 2.1.1 Proposal for installation

M 1: A technical proposal for the installation for both phases including a detailed arrangement plan must be submitted.

Answers and annotations by the vendor:

[Insert text here]

#### 2.1.2 Date of Installation

| M 2: | Detailed information about:                                                                 |

|------|---------------------------------------------------------------------------------------------|

|      | - the earliest installation date of Phase 1                                                 |

|      | - the earliest installation date of Phase 2                                                 |

|      | - the time needed to complete the installations                                             |

|      | <ul> <li>the length of interruption of service needed for the upgrade to Phase 2</li> </ul> |

|      | must be submitted.                                                                          |

Answers and annotations by the vendor:

[Insert text here]

#### 2.1.3 Delivery to the place of installation

The offered system shall be installed in the designated computer room of the new LRZ building. The freight elevator has clearance dimensions of

- width x height x depth = 1,55 m x 2.25 m x 2.25 m

- and a maximum payload of 2000 kg (~ 20 kN).

- I 1: The transportation of the offered system to the place of installation should be feasible under the above mentioned conditions

1

Check here if the requirement can be fulfilled:

#### 2.1.4 Installation of the system

An area in the new computer room of LRZ, which is specified in the floor plan included with the tender documents, is reserved for the system to be offered. The computer room is free of pillars and has the following dimensions and false floor specifications:

- width x depth x height =  $28 \text{ m x } 21 \text{ m x } 8 \text{ m} (= 588 \text{ m}^2 \text{ x } 8 \text{ m})$

- false floor with a maximum area load of 1500 kg per m<sup>2</sup> (~ 15 kN/m<sup>2</sup>), a maximum "*point load*" of 500 kg and a height of 1.8 m

| M 3: | Both installation phases of the offered system must be installable i computer room of LRZ.                                                                            | n the designated |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

|      | Check here if the requirement can be fulfilled:                                                                                                                       | []               |

|      |                                                                                                                                                                       |                  |

| M 4: | The dimensions (i.e., foot print), maintenance areas, and weights of the submitted and they must be within specifications for the computer room                       |                  |

|      | Check here if the requirement can be fulfilled:                                                                                                                       | []               |

|      |                                                                                                                                                                       |                  |

| M 5: | By checking the box, the vendor declares that the complete installa preparation for operation of the HLRB II (for both installation phases) the vendor <sup>2</sup> . |                  |

|      |                                                                                                                                                                       |                  |

#### 2.1.5 Power supply and conformity with electrical standards

LRZ provides power supply of 50 Hz alternating current, with 230 V single-phase and 400 V three-phase voltages, as commonly available in Germany. The planning and installation of electrical power and cooling equipment needed to run both phases will be performed during 2005.

| I 2: | The total electrical power consumption of the combined Phases 1+2 of should not exceed 1800 kVA. <sup>3</sup> | of the HLRB II  |

|------|---------------------------------------------------------------------------------------------------------------|-----------------|

|      | Check here if the requirement can be fulfilled:                                                               | []              |

|      |                                                                                                               |                 |

| I 3: | The offered system configuration for the HLRB II in both installation phase trically connected and operated.  | es can be elec- |

|      | Check here if the requirement can be fulfilled:                                                               | []              |

If other electrical power characteristics should be needed, the required frequency and voltage transformers must be included in the tender. The requirements for their installation (space demand, environmental conditions, and maximum distance to the HLRB II) must be specified in detail. The installation of such components is part of the installation of the HLRB II and cannot be charged separately.

M 6: The characteristics of the power supply (e.g., voltage, number of phases, frequency) and the expected and peak energy consumption (in kVA) must be specified.

The appropriate fields in the table at the end of this document must be filled in.

The *EC Directive on Electromagnetic Compatibility of Devices* is the guideline for all manufacturers, importers, and distributors of electric and electronic devices in the European Union as far as development, production and distribution of devices, systems and equipment are concerned. In addition, the *Low-Voltage Directives 73/23/EEC* and the *Act about Product Liability* must be considered.

These regulations and the corresponding directives and standards are EU stipulations that have been adopted by German Law.

By attaching a "CE marking" on a device, the manufacturer gives a legally binding declaration that the device conforms with all EMC relevant directives and standards of the EU and with the regulations and laws.

<sup>&</sup>lt;sup>2</sup>LRZ only lends the necessary technical support.

<sup>&</sup>lt;sup>3</sup> cf. cover letter ("Anschreiben")

M 7: The devices must conform to German and European directives, i.e., they need to pass tests for the EC Directive on Electromagnetic Compatibility 89/336/EEC, Category A of limitation of interfering radiation (see EN55022-1998) and the above mentioned Low-Voltage Directives 73/23/EEC. All necessary documentation will be submitted to LRZ before delivery of the system.

Check here if the requirement can be fulfilled:

- r ۱

- T 1: Classification in Category B of limitation of interfering radiation and CE-marking are desired.

Check here if the requirement can be fulfilled:

#### 2.1.6 Environmental conditions

M 8: The required environmental conditions (e.g., ambient temperature, humidity, dust free conditions, etc.) for the main system and the peripheral devices must be specified.

The appropriate fields in the table at the end of this document must be filled in.

M 9: The type of cooling system for all devices (air-cooling, water-cooling, etc.) and details about the cooling system (e.g., in- and outlet temperature, temperature variation tolerance, purity requirements, etc.) must be specified.

The appropriate fields in the table at the end of this document must be filled in.

M 10: The heat emission of all devices of the offered system, broken down into air and water cooling, i.e., the maximum values and estimated values for permanent load, must be specified.

The appropriate fields in the table at the end of this document must be filled in.

I 4: The total heat emission for the combined Phases 1+2 should not exceed 1800 kW.<sup>4</sup> Check here if the requirement can be fulfilled:

# **2.1.7** Fire detection and protection

In case of fire, the computer room for the HLRB II can be flooded with inert gas. However, doing this is very expensive. Therefore fire protection, detection and/or extinction devices within the system are desired.

| T 2: | Internal fire detection devices are provided.                        |    |

|------|----------------------------------------------------------------------|----|

|      | Check here if the requirement can be fulfilled:                      | [] |

| -    |                                                                      |    |

| T 3: | Internal fire protection devices are provided.                       |    |

|      | Check here if the requirement can be fulfilled:                      | [] |

|      |                                                                      |    |

| T 4: | Fire extinguishing agents which do not harm the system are provided. |    |

|      | Check here if the requirement can be fulfilled:                      | [] |

If provided, describe the means of fire protection/detection/extinction in detail.

<sup>&</sup>lt;sup>4</sup> cf. cover letter ("Anschreiben")

List the recommended fire extinguishing agents.

Answers and annotations by the vendor:

[Insert text here]

# 2.2 Hardware of the compute nodes

#### 2.2.1 Compute node architecture

M 11: A detailed description of the compute node architecture (node architecture, processor architecture, etc.) is required.

The appropriate fields in the table at the end of this document must be filled in.

Additionally, the specifications of all components must be explained in detail and the following items must be considered:

- general description of architecture

- technology

- number of offered compute nodes, number of processors and size of main memory

- clock rates, number of floating and fixed point operations per clock (separately for scalar and/or vector)

- number of registers (separately for floating point, integer and general purpose operations, and for scalar and/or vector operations)

- number of execution units (e.g., arithmetic and general purpose units)

- if vector units are available, describe which data types are vectorized

#### Answers and annotations by the vendor:

[Insert text here]

# 2.2.2 Performance of the SMP compute nodes

According to the target group of applications for the HLRB II only nodes with high individual performance will be considered.

The offered compute nodes must achieve a minimum compute performance (optionally obtained by auto-vectorization and/or auto-parallelization and/or OpenMP directives) which is described in the benchmark-ing chapter (see section 4). Therefore:

# I 5: All compute nodes should consist of SMP nodes with 8 or more CPUs. Check here if the requirement can be fulfilled: []

If you cannot fulfill this requirement, please explain why the offered nodes are suitable for the outlined designated usage of the system.

Answers and annotations by the vendor:

### 2.2.3 Extent of inhomogeneity of installation Phases 1 and 2

The HLRB II may be inhomogeneous in the two installation phases, e.g., processors of different clock frequency may be used for Phase 1 and Phase 2 and/or shared memory nodes with different numbers of CPUs may be used.

The transfer of applications between Phase 1 and 2 must be easily and readily possible. The intention of this is not to limit the option of having individual tuning and compiler parameters for a particular phase, but to make it possible to run a suitably generated executable on any of the two phases of the system.

In any case, the second phase installation must not result in an essential change of the programming paradigm, i.e., programs that achieve their computing performance by automatic parallelization and/or automatic vectorization, must run with a comparable efficiency and without major alterations at the program source level.

| M 12: | It must be possible to run a suitably compiled executable on any comp<br>entire system.                                                        | ute node of the |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|       | Check here if the requirement can be fulfilled:                                                                                                | []              |

| M 13: | It must be possible to run a single program across the entire system.                                                                          |                 |

|       | Check here if the requirement can be fulfilled:                                                                                                | []              |

|       |                                                                                                                                                |                 |

| M 14: | It must be possible to access all relevant user file systems on the NA equal efficiency from both phases (see 2.4.1).                          | S storage with  |

|       | Check here if the requirement can be fulfilled:                                                                                                | []              |

|       |                                                                                                                                                |                 |

| I 6:  | It should be possible to access all relevant parallel file systems on the SA with approximately equal efficiency from both phases (see 2.4.1). | N/DAS storage   |

|       | Check here if the requirement can be fulfilled:                                                                                                | []              |

If it is not obvious in itself, please explain how these requirements are fulfilled.

Answers and annotations by the vendor:

[Insert text here]

#### 2.2.4 Size of main memory

The offered main memory must have appropriate size and bandwidth in relation to the compute performance of the nodes.

In accordance to the observed user needs, the size of the memory available for user programs should satisfy the following criteria:

| M 15: | M 15: The relative size of the main memory of a node must be at least 0.5 Byte per Flop/s theoretical peak performance. |          |      |               |       |         |      |      |    |    |       |

|-------|-------------------------------------------------------------------------------------------------------------------------|----------|------|---------------|-------|---------|------|------|----|----|-------|

|       | Check here if the requirement can be fulfilled:                                                                         |          |      |               |       |         |      |      |    |    |       |

| M 16: | The minimum 32 GBytes.                                                                                                  | amount   | of   | memory        | per   | compute | node | must | be | at | least |

|       | Check here if the                                                                                                       | requirem | ento | can be fulfil | lled: |         |      |      | ]  | ]  |       |

If the operating system or buffers for message passing etc. need a substantial fraction of the main memory, the vendor should disclose this information and take it into account in his offer, i.e. provided more than the required minimum.

However, if the vendor offers a substantially larger memory than required, this will not automatically be honored by LRZ's evaluation criteria. Therefore the vendor should explain the rationale behind this over-commitment.

Answers and annotations by the vendor:

[Insert text here]

#### 2.2.5 Bandwidth of main memory

# I 7: The theoretical bandwidth of a node should exceed the value of 1 Byte/s per Flop/s theoretical peak performance.

Check here if the requirement can be fulfilled:

[]

However, the required bandwidth for many scientific applications is well above 3 Byte/s theoretical bandwidth per theoretical Flop/s. Therefore substantially larger bandwidth to memory than the required one will be positively honored by the LRZ evaluation scheme.

T 5: It is desired that the relative bandwidth of a node exceed 3 Byte/s theoretical bandwidth per Flop/s theoretical peak performance.

Check here if the requirement can be fulfilled: []

The need for bandwidth to the local memory can be partially compensated by very large caches, therefore:

T 6: For systems with low memory bandwidth, it is desired that the size of the largest cache exceeds 6 MB per CPU.

Check here if the requirement can be fulfilled:

#### 2.2.6 Memory and cache hierarchy

M 17: The vendor must disclose detailed information about the memory subsystem and, if applicable, of the cache hierarchy of the compute nodes, i.e.,

- latencies

- bandwidths

- size and associativity of caches and/or vector registers

- access patterns (cache line sizes, maximum number of outstanding prefetches, memory interleaving, etc.)

- TLB size (entries) and latency

The appropriate fields in the table at the end of this document must be filled in.

Additionally, the following information should be disclosed:

- the influence of a stride different from one on memory access time

- possibilities of memory conflicts and the delays they will cause (locally, on the node, and over the whole network).

- special hardware characteristics that support operations on sparse matrices or indirect addressing (Gather/Scatter or similar)

- number of processors that can access the shared main memory without significant delay, if each processor requires the maximum memory bandwidth with respect to its memory bus

- the structure of address space of the system must be indicated.

- the cache coherency should be described (i.e., cc-NUMA<sup>5</sup> or non-cc-NUMA).

- the policies for data placement (e.g., first touch, page migration)

Answers and annotations by the vendor:

[Insert text here]

# 2.2.7 Memory protection and error detection

Check here if the requirement can be fulfilled:

| M 18: | Mechanisms for error detection and correction in main memory must be provided. |  |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------|--|--|--|--|--|--|

|       | Check here if the requirement can be fulfilled:                                |  |  |  |  |  |  |

|       |                                                                                |  |  |  |  |  |  |

| T 7:  | Extended memory protection mechanisms (like Chipkill) are desired.             |  |  |  |  |  |  |

Please describe these mechanisms.

Answers and annotations by the vendor:

[Insert text here]

# 2.2.8 Hardware support of parallelization

| T 8: | Fast hardware synchronization to support SMP-parallelization within a node |    |  |  |  |  |  |

|------|----------------------------------------------------------------------------|----|--|--|--|--|--|

|      | Check here if the requirement can be fulfilled:                            | [] |  |  |  |  |  |

If available, please describe.

What are the available hardware characteristics to support parallelization between nodes (e.g., RDMA, global address space etc.) ?

Answers and annotations by the vendor:

[Insert text here]

# 2.3 Communication network

#### 2.3.1 Hardware of internal interconnect

M 19: A detailed description of the internal interconnect within Phase1 and Phase 2, as well as of the interconnect between the two phases must be given.

The appropriate fields in the table at the end of this document must be filled in.

The following items should be disclosed:

- general description of network structure and node connections

- technology

<sup>&</sup>lt;sup>5</sup> ccNUMA = cache coherent Non Uniform Memory Access

- topology

- bandwidth and latency (where appropriate, taking into account distance between nodes)

- scalability with number of compute nodes

- performance of all involved single components

- limitations (e.g., message length, number of outstanding messages)

- maximum time for a broadcast to reach all nodes

Answers and annotations by the vendor:

[Insert text here]

# 2.3.2 Interconnect within Phase 1 or within Phase 2

The performance of the interconnect within Phase 1 and within Phase 2, respectively, must be in appropriate relation to the compute performance of the nodes.

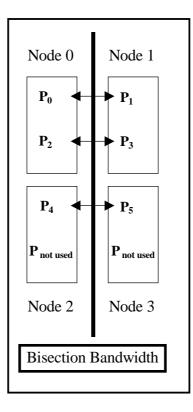

| l 8:  | The interconnect balance                                                                                                                                                                                                              |                 |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|       | <ul> <li>aggregate MPI link bandwidth (Byte/s) of a node         <ul> <li>(as defined by the MPI benchmark in 4.1.2)</li> <li>divided by</li> <li>the weighted performance of the vector triad (Flop/s) of a node</li></ul></li></ul> |                 |

|       | should exceed 0.4 Byte/s/Flop/s.                                                                                                                                                                                                      |                 |

|       | Check here if the requirement can be fulfilled:                                                                                                                                                                                       | []              |

| T 9:  | It is desired that the interconnect balance of one node (as defined above<br>Bytes/s per Flop/s                                                                                                                                       | e) exceeds 0.8  |

|       | Check here if the requirement can be fulfilled:                                                                                                                                                                                       | []              |

| T 10: | It is desired that the theoretical (neak) interconnect handwidth of one ned                                                                                                                                                           | o ovocado 5%    |

| 1 10. | It is desired that the theoretical (peak) interconnect bandwidth of one nod of the theoretical memory bandwidth of that node.                                                                                                         | e exceeds 5%    |

|       | Check here if the requirement can be fulfilled:                                                                                                                                                                                       | []              |

| M 20: | The MPI latency, between two arbitrary nodes within Phase 1 or between nodes within Phase 2 must not exceed 8 $\mu$ s.                                                                                                                | n two arbitrary |

|       | Check here if the requirement can be fulfilled:                                                                                                                                                                                       | []              |

| T 11: | It is desired that the MPI latency between two arbitrary nodes within any p                                                                                                                                                           | hase does not   |

|       | exceed 5 µs.                                                                                                                                                                                                                          |                 |

|       | Check here if the requirement can be fulfilled:                                                                                                                                                                                       | []              |

#### 2.3.3 Interconnect between Phase 1 and Phase 2

The interconnect between the two phases of HLRB II may be different from that within Phase 1 or Phase 2, respectively. Notwithstanding, starting a parallel program across phase boundaries must be possible in a transparent manner.

One important aspect for the interconnect between the two phases is to handle the I/O traffic. This defines a lower limit for the required bandwidth.

M 21: The MPI bidirectional bisection bandwidth between Phase 1 and Phase 2 as defined by the benchmark in 4.1.4 must exceed 80 GByte/s (40 GByte/s in each direction). Check here if the requirement can be fulfilled:

I 9: The MPI latency across the phase boundaries between two arbitrary nodes should not exceed 10 μs. []

Check here if the requirement can be fulfilled:

T 12: It is desired that the interconnect between the two phases is of the same type and characteristics as within a phase.

Check here if the requirement can be fulfilled:

# 2.3.4 Control network

Are there, besides the internal interconnect for data exchange in user programs, other internal networks (e.g., for system purposes)? If yes, please describe their structure and function.

Answers and annotations by the vendor:

[Insert text here]

#### 2.3.5 Connection to external network

| l 10: | 10 Gigabit ethernet (10 GE) interfaces with TCP/IP offload functionality (TO functionality should be delivered as communication interfaces for connecting to the outside world for both phases.                         | ,          |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|       | Check here if the requirement can be fulfilled:                                                                                                                                                                         | []         |

|       |                                                                                                                                                                                                                         |            |

| M 22: | At least two independent network connections to the external network using<br>ethernet frame size of 1500 Bytes must be provided for each phase.                                                                        | a standard |

|       | Check here if the requirement can be fulfilled:                                                                                                                                                                         | []         |

|       |                                                                                                                                                                                                                         |            |

| M 23: | The external network connection of the system is considered to be balance<br>measurable bandwidth of more than 600 MByte/s to the NAS filer for Pha<br>MByte/s for Phase 2 according to IO-Bench 2 (see section 4.2.2). |            |

|       | Check here if the requirement can be fulfilled:                                                                                                                                                                         | []         |

A detailed description of the available external 10 GE communication interfaces (or statements about their planned availability) with all relevant performance specifications (hardware and typical achievable values under TCP/IP protocol stack as well as port trunking support, cable type and maximum cable length) is required.

Answers and annotations by the vendor:

# 2.4 Disk storage

#### 2.4.1 User disk storage

Two different types of user mass storage have to be delivered with HLRB II:

- a parallel, high-performance file system with very high aggregate bandwidth, which can be accessed by every node (Storage Area Network/Direct Attached Storage, SAN/DAS)

- a Network Attached Storage (NAS) connected over Gigabit Ethernet or 10 Gigabit Ethernet and **NFSv3** or higher, to ensure a high interoperability with applications outside the HLRB II.

| M 24: | All user mass storage has to be RAID-protected, using at least RAID levels RAID1, RAID3, RAID4, RAID5 or higher.                                                                                                                                                                                                                                                                                   |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | One or more spare disks with automatic take-over, redundant controllers with mirrored or deactivated controller caches must be provided.                                                                                                                                                                                                                                                           |

|       | Check here if the requirement can be fulfilled:                                                                                                                                                                                                                                                                                                                                                    |

| M 25: | A net value of at least 300 TByte <sup>6</sup> SAN/DAS mass storage has to be delivered for each phase.                                                                                                                                                                                                                                                                                            |

|       | Check here if the requirement can be fulfilled:                                                                                                                                                                                                                                                                                                                                                    |

| I 11: | It should be possible that a single (parallel) file system serves this storage to the users for each of the phases.                                                                                                                                                                                                                                                                                |

|       | Check here if the requirement can be fulfilled:                                                                                                                                                                                                                                                                                                                                                    |

| I 12: | The storage systems should support scheduled media scans with configurable priority<br>and manual or automatic cloning of disk drives showing an increasing number of bad<br>blocks.                                                                                                                                                                                                               |

|       | Check here if the requirement can be fulfilled:                                                                                                                                                                                                                                                                                                                                                    |

| M 26: | A net value of at least 40 TByte <sup>7</sup> of Network Attached Storage must be delivered with<br>Phase 1 and additional 20 TByte <sup>8</sup> of Network Attached Storage have to be delivered with<br>Phase 2 of HLRB II.<br>For this type of user storage a disk technology built for high I/O rates has to be used, i.e.,<br>native SCSI, Fibre Channel or Serial Attached SCSI disks (SAS). |

|       | Check here if the requirement can be fulfilled:                                                                                                                                                                                                                                                                                                                                                    |

| I 13: | It should be possible that all NAS capacity is accessible in a single file system.                                                                                                                                                                                                                                                                                                                 |

|       | Check here if the requirement can be fulfilled:                                                                                                                                                                                                                                                                                                                                                    |

| I 14: | The Network Attached Storage should be implemented as a <b>highly available</b> stand-<br>alone solution, e.g., it should be possible to access all data on this storage from outside<br>independent from the status of the HLRB II.                                                                                                                                                               |

<sup>&</sup>lt;sup>6</sup> In this context 1 TByte is defined as 10<sup>12</sup> Bytes

<sup>&</sup>lt;sup>7</sup> In this context 1 TByte is defined as 10<sup>12</sup> Bytes

<sup>&</sup>lt;sup>8</sup> In this context 1 TByte is defined as 10<sup>12</sup> Bytes

In addition it should be possible to access all NAS data from outside using a standard ethernet frame size of 1500 bytes. Check here if the requirement can be fulfilled: [] The NAS solution should provide an automatic as well as a manual file system snap-I 15: shot functionality and should support an automatic replication (and different levels of synchronicity) of the snapshots over SAN and/or LAN to one or more other network filer. Check here if the requirement can be fulfilled: ſ 1 The NAS solution should support data backup using NDMP together with Tivoli Storage I 16 Management (TSM) servers (see also 2.9.2). Check here if the requirement can be fulfilled: [] M 27: The offered I/O solutions and disk technologies must be described in detail.

The description should contain information about

- the expected MTBF of the single devices

- capacity

- number of drives

- redundancy

- used channel protocol

- peak, average, and sustainable transfer rates and access times

- how disk errors will be reported by the operating system.

- a detailed description of the SAN/DAS solution containing all relevant features, such as hardware specifications, reliability, management software and interfaces, functionalities for protection against data loss (e.g., number of spare disks, supported RAID levels, snapshots and replication).

- a detailed description of the NAS solution containing all relevant features, such as hardware specifications, reliability, management software and interfaces, functionalities for protection against data loss (e.g., number of spare disks, supported RAID levels (double parity), snapshots, replication, fast backup and restore of data ).

Answers and annotations by the vendor:

[Insert text here]

# 2.4.2 Disk storage containing the operating system, swap and/or paging space of the nodes

M 28: All disk storage containing the operating system, swap and/or paging space of the nodes has to be RAID-protected, using RAID-level RAID1 or higher. Check here if the requirement can be fulfilled:

M 29: The offered disk capacity and technology must be described.

Answers and annotations by the vendor:

#### 2.4.3 I/O nodes

# M 30: I/O nodes (or nodes specially equipped for I/O) and their input/output channels must be described.

The description must include:

- general description of architecture, including performance specifications

- technology

- number of offered nodes, their equipment with processors and main memory

- procedure for adding I/O nodes

- maximum possible number of I/O nodes.

Answers and annotations by the vendor:

[Insert text here]

#### 2.4.4 Management tools for the disk subsystem

| T 13: | Graphical management tools for the disk system are desired. |    |

|-------|-------------------------------------------------------------|----|

|       | Check here if the requirement can be fulfilled:             | [] |

If available, please describe them.

Answers and annotations by the vendor:

[Insert text here]

# 2.5 Hardware faults

#### 2.5.1 Detection of hardware faults

M 31: Facilities for the online detection of hardware errors (e.g., faulty memory modules, processors, fans, network links, switches) must be available.

Check here if the requirement can be fulfilled:

Particularly describe:

- the facilities for diagnosis and error correction

- the process of diagnosis and error correction

- whether there are any spare nodes or spare processors and what their functions are

- whether faulty nodes or processors can be taken out of service without interruption of operation and, if necessary, be substituted by spare nodes or spare processors

- whether error correction can be carried out online

Answers and annotations by the vendor:

[Insert text here]

1

# 2.5.2 Mean time between failures

M 32: An estimate and rationale for the expected mean time between failures (MTBF) of the overall system and its major components must be given.

Answers and annotations by the vendor:

[Insert text here]

# 2.6 Operating system

If the operating system (partially) runs on a front-end computer the following requirements must be explained in the tender for the supercomputer itself as well as for the front-end computer, wherever this is reasonable.

System components for resource administration and batch administration as well as other components that are essential for system operation are considered part of the operating system even if, formally, the manufacturer (or another vendor) should offer them separately.

#### 2.6.1 64-bit operating system

| M 33: | The system must be delivered with a 64-bit operating system using a 64-bit | t kernel. |

|-------|----------------------------------------------------------------------------|-----------|

|       | Check here if the requirement can be fulfilled:                            | []        |

Please describe the 64-bit implementation details.

Answers and annotations by the vendor:

[Insert text here]

#### 2.6.2 Standards

| M 34: | The operating system must be complete, stable and appropriate for production usage in a supercomputing center, i.e., it must allow flexible administration and control of interactive and batch mode. |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Check here if the requirement can be fulfilled:                                                                                                                                                       |

| I 17: | The operating system should be based on UNIX or Linux and should be compatible with the X/Open Standard POSIX 1003 (ISO/IEC 9945).                                                                    |

|       | Check here if the requirement can be fulfilled:                                                                                                                                                       |

Answers and annotations by the vendor:

# 2.6.3 Stability

Since the HLRB II will usually run 24 hours a day, high system stability and easy recoverability is of great importance. Special attention has to be paid to the problem of interruptions due to hardware failures.

| M 35: | In case of a failure of a compute or I/O node a seamless degradation of the be warranted. | system must |

|-------|-------------------------------------------------------------------------------------------|-------------|

|       | Check here if the requirement can be fulfilled:                                           | []          |

Please describe in detail how the operation of the system with lower performance in case of failure of a component (e.g., a CPU, a compute node, an I/O node, a part of the main memory, a part of the disks) will be guaranteed.

Please describe how the repaired components will be returned to operation. In which cases is this possible without interruption of normal operations, in which cases can an interruption not be avoided?

Describe which components may cause an interruption of the complete system.

Answers and annotations by the vendor:

[Insert text here]

#### 2.6.4 Checkpointing

As a provision against unplanned interrupts the possibility of checkpoint/restart is desired.

| T 14: | The possibility of user initiated checkpoint/restart is desired.   |    |

|-------|--------------------------------------------------------------------|----|

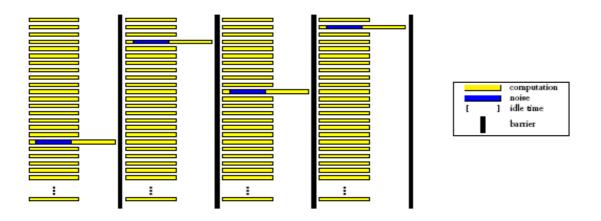

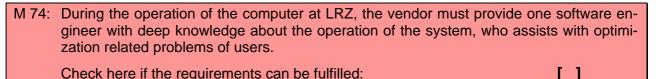

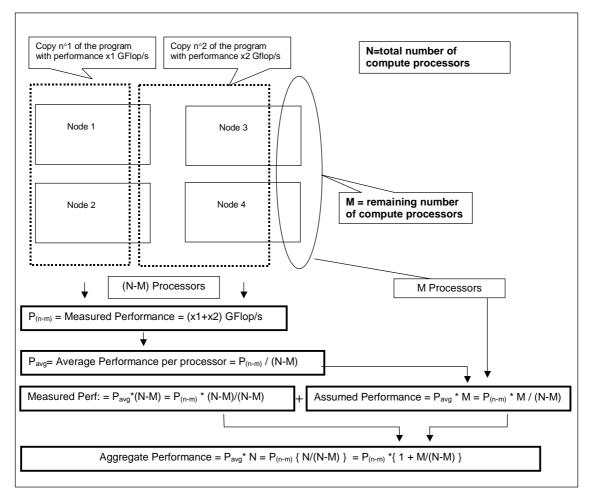

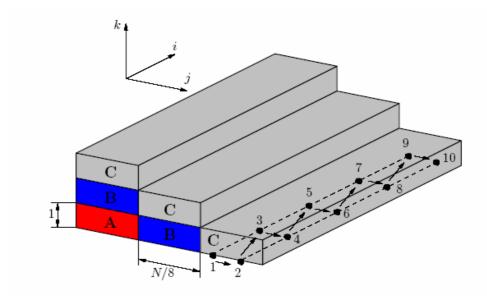

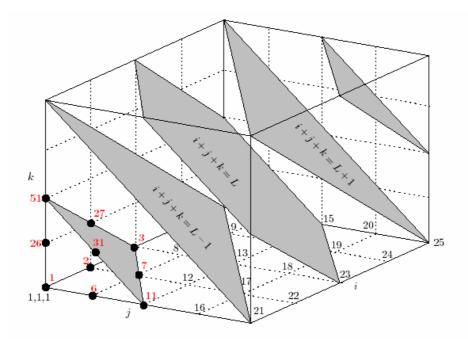

|       | Check here if the requirement can be fulfilled:                    | [] |